- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377905 > MB89490 (Fujitsu Limited) 8-bit Proprietary Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | MB89490 |

| 廠商: | Fujitsu Limited |

| 元件分類: | 8位微控制器 |

| 英文描述: | 8-bit Proprietary Microcontroller |

| 中文描述: | 8位微控制器專有 |

| 文件頁(yè)數(shù): | 3/45頁(yè) |

| 文件大小: | 577K |

| 代理商: | MB89490 |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)

3

MB89490 Series

*1 : I

2

C is complied to Philips I

2

C specification.

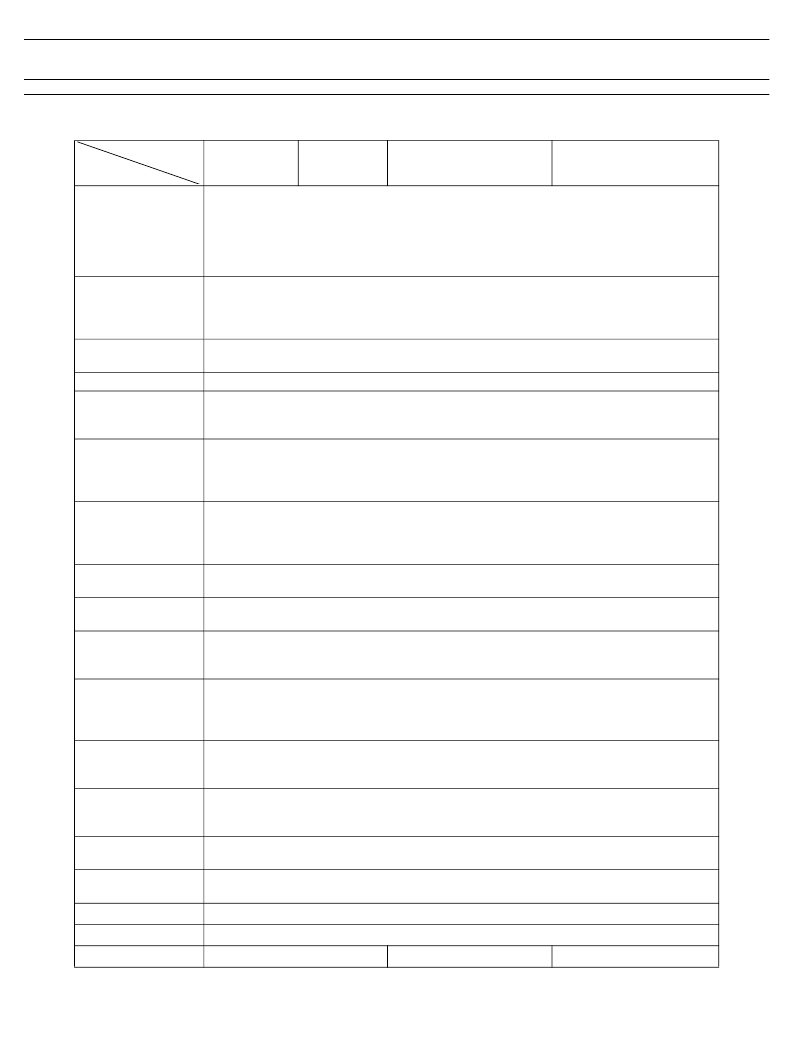

MB89497

MB89498

MB89F499

MB89PV490

CPU functions

Number of instructions

Instruction bit length

Instruction length

Data bit length

Minimum execution time

Minimum interrupt processing time

I/O ports (CMOS)

Input ports (CMOS)

N-channel open drain I/O ports

Total

: 136

: 8 bits

: 1 to 3 bytes

: 1, 8, 16 bits

: 0.32

μ

s/12.5 MHz

: 2.88

μ

s/12.5 MHz

: 56 pins

: 2 pins

: 8 pins

: 66 pins

Ports

21-bit timebase

timer

Watchdog timer

Interrupt period (0.66 ms, 2.6 ms, 21.0 ms, 335.5 ms) at 12.5 MHz

Reset period (167.8 ms to 335.5 ms) at 12.5 MHz.

8-bit reload timer operation (supports square wave output, operating clock period: 1, 8, 16, 64

t

inst

,)

8-bit resolution PWM operation

Can be operated either as a 2-channel 8-bit timer/counter (timer 00 and timer 01, each with its

own independent operating clock cycle), or as one 16-bit timer/counter

In timer 00 or 16-bit timer/counter operation, event counter operation (external clock-triggered)

and square wave output capability

Can be operated either as a 2-channel 8-bit timer/counter (timer 10 and timer 11, each with its

own independent operating clock cycle), or as one 16-bit timer/counter

In timer 10 or 16-bit timer/counter operation, event counter operation (external clock-triggered)

and square wave output capability

PWM timer 0,1

8/16-bit timer/

counter 00, 01

8/16-bit timer/

counter 10, 11

External interrupt 0

(edge)

External interrupt 1

(level)

8 independent channels (selectable edge, interrupt vector, request flag)

8 channels (low level interrupt)

A/D converter

10-bit resolution

×

8 channels

A/D conversion function (conversion time: 38 t

inst

)

Supports repeated activation by internal clock

LCD controller/driver

Common output

Segment output

Bias power supply pins

LCD display RAM size

Synchronous/asynchronous data transfer capability

(Max. baud rate: 97.656 Kbps at 12.5 MHz)

(7 and 8 bits with parity bit; 8 and 9 bits without parity bit)

8-bit serial I/O with LSB first/MSB first selectability

One clock selectable from four operation clock (one external shift clock, three internal shift

clock: 0.64

μ

s, 2.56

μ

s, 10.24

μ

s at 12.5MHz)

1 channel

Use a 2-wire protocol to communicate with other device

Selectable maximum noise width removal

Reversible input polarity

: 4 (max.)

: 32 (max.)

: 3

: 32

×

4 bits

UART/SIO

SIO

I

2

C

*1

Remote receiver

Standby mode

Sleep mode, stop mode, watch mode, sub-clock mode

Process

CMOS

Operating voltage

2.2V ~ 3.6V

2.7V ~ 3.6V

2.7V ~ 3.6V

Part number

Parameter

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB89497 | 8-bit Proprietary Microcontroller |

| MB89497PF | 8-bit Proprietary Microcontroller |

| MB89498 | 8-bit Proprietary Microcontroller |

| MB89498PF | 8-bit Proprietary Microcontroller |

| MB89F499 | 8-bit Proprietary Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB89490_03 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontroller CMOS |

| MB89497 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontroller |

| MB89497PF | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontroller |

| MB89498 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontroller |

| MB89498PF | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。