- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377918 > MB90F474H (Fujitsu Limited) 16-Bit Proprietary Microcontroller PDF資料下載

參數(shù)資料

| 型號: | MB90F474H |

| 廠商: | Fujitsu Limited |

| 英文描述: | 16-Bit Proprietary Microcontroller |

| 中文描述: | 16位微控制器專有 |

| 文件頁數(shù): | 26/118頁 |

| 文件大小: | 555K |

| 代理商: | MB90F474H |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁

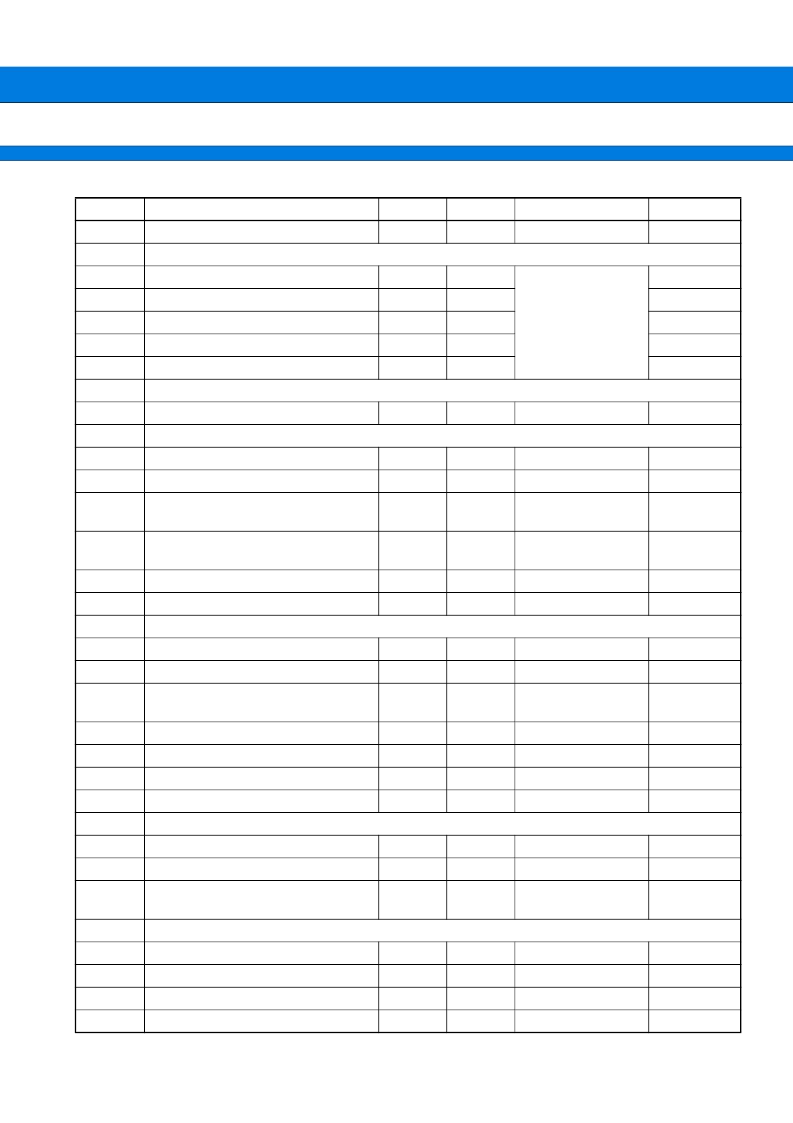

MB90470 Series

26

(Continued)

Address

Register name

Symbol

Access

Resource name

Default

86

H

PWC2 division ratio register

DIVR2

R/W

PWC (ch2)

- - - - - - 0 0

87

H

Reserved

88

H

I

2

C bus status register

IBSR

R

I

2

C functions

0 0 0 0 0 0 0 0

89

H

I

2

C bus control register

IBCR

R/W

0 0 0 0 0 0 0 0

8A

H

I

2

C bus clock select register

ICCR

R/W

- - 0XXXXX

8B

H

I

2

C bus address register

IADR

R/W

- XXXXXXX

8C

H

I

2

C bus data register

IDAR

R/W

XXXXXXXX

8D

H

Reserved

8E

H

μ

PG control register

PGCSR

R/W

μ

PG

0 0 0 0 0 - - -

8F

H

to 9B

H

Prohibited

9C

H

μ

DMA status register

μ

DMA status register

Program address detection control

status resister

DSRL

R/W

μ

DMA

μ

DMA

0 0 0 0 0 0 0 0

9D

H

DSRH

R/W

0 0 0 0 0 0 0 0

9E

H

PACSR

R/W

Address Match

Detection Function

0 0 0 0 0 0 0 0

9F

H

Delay interrupt source generate/

release register

DIRR

R/W

Delay interrupt

generator module

- - - - - - - - 0

A0

H

Low power mode register

LPMCR

R/W

Low power modes

0 0 0 1 1 0 0 0

A1

H

Clock select register

CKSCR

R/W

Low power modes

1 1 1 1 1 1 0 0

A2

H

, A3

H

Reserved

A4

H

μ

DMA stop status register

Auto ready function select register

DSSR

R/W

μ

DMA

0 0 0 0 0 0 0 0

A5

H

ARSR

W

External pins

0 0 1 1 - - 0 0

A6

H

External address output control

register

HACR

W

External pins

0 0 0 0 0 0 0 0

A7

H

Bus control signal control register

EPCR

W

External pins

1 0 0 0 * 1 0 -

A8

H

Watchdog control register

WDTC

R/W

Watchdog timer

XXXXX 1 1 1

A9

H

Time base timer control register

TBTC

R/W

Time base timer

1 X X 0 0 1 0 0

AA

H

Watch timer control register

WTC

R/W

Watch timer

1 0 0 0 1 0 0 0

AB

H

Reserved

AC

H

μ

DMA control register

μ

DMA control register

DERL

R/W

μ

DMA

μ

DMA

0 0 0 0 0 0 0 0

AD

H

DERH

R/W

0 0 0 0 0 0 0 0

AE

H

Flash memory control status register

FMCR

R/W

Flash memory

interface

0 0 0 X 0 0 0 0

AF

H

Prohibited

B0

H

Interrupt control register 00

ICR00

R/W

XXXX 0 1 1 1

B1

H

Interrupt control register 01

ICR01

R/W

XXXX 0 1 1 1

B2

H

Interrupt control register 02

ICR02

R/W

XXXX 0 1 1 1

B3

H

Interrupt control register 03

ICR03

R/W

XXXX 0 1 1 1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB90F474HPF | 16-Bit Proprietary Microcontroller |

| MB90F474HPFV | 16-Bit Proprietary Microcontroller |

| MB90F474L | 16-Bit Proprietary Microcontroller |

| MB90F474LPF | 16-Bit Proprietary Microcontroller |

| MB90F474LPFV | 16-Bit Proprietary Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB90F474HPF-GE1 | 制造商:FUJITSU 功能描述:IC 16BIT MCU I2C SMD QFP100 |

| MB90F474HPFR-GE1 | 制造商:FUJITSU 功能描述: |

| MB90F474HPMC-GE1 | 制造商:FUJITSU 功能描述: |

| MB90F474LPFR-GE1 | 制造商:FUJITSU 功能描述: |

| MB90F474LPMCR-GE1 | 制造商:FUJITSU 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。