- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄45198 > MB95F582HWQN-G-JNERE1 (FUJITSU LTD) MICROCONTROLLER, PQCC32 PDF資料下載

參數(shù)資料

| 型號(hào): | MB95F582HWQN-G-JNERE1 |

| 廠商: | FUJITSU LTD |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | MICROCONTROLLER, PQCC32 |

| 封裝: | 5 X 5 MM, 0.80 MM HEIGHT, PLASTIC, M19, QFN-32 |

| 文件頁(yè)數(shù): | 57/84頁(yè) |

| 文件大小: | 3929K |

| 代理商: | MB95F582HWQN-G-JNERE1 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)當(dāng)前第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)

MB95560H/570H/580H Series

60

DS702-00010-1v0-E

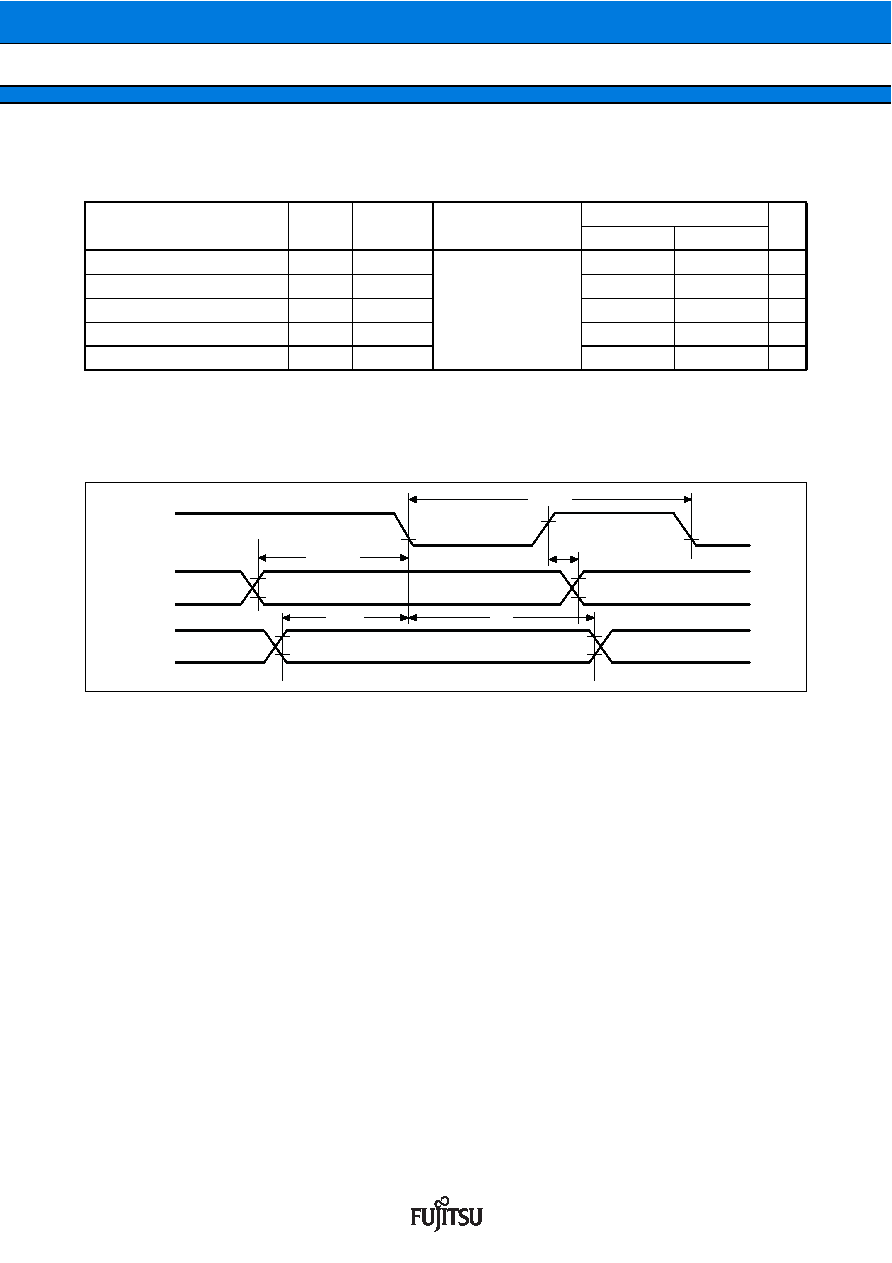

Sampling is executed at the rising edge of the sampling clock*1, and serial clock delay is enabled*2.

(ESCR register: SCES bit = 0, ECCR register: SCDE bit = 1)

(VCC = 5.0 V

± 10%, VSS = 0.0 V, TA = 40°C to + 85°C)

*1: There is a function used to choose whether the sampling of reception data is performed at a rising edge or

a falling edge of the serial clock.

*2: The serial clock delay function is a function that delays the output signal of the serial clock for half clock.

Parameter

Symbol Pin name

Condition

Value

Unit

Min

Max

Serial clock cycle time

tSCYC

SCK

Internal clock

operation output pin:

CL = 80 pF

+ 1 TTL

5 tMCLK*3

—ns

SCK

↑→ SOT delay time

tSHOVI

SCK, SOT

50

+ 50

ns

Valid SIN

→ SCK ↓

tIVSLI

SCK, SIN

tMCLK*3

+ 80

—

ns

SCK

↓→ valid SIN hold time

tSLIXI

SCK, SIN

0

—

ns

SOT

→ SCK ↓ delay time

tSOVLI

SCK, SOT

3 tMCLK*3

70

—

ns

0.8 VCC

0.2 VCC

tSHOVI

tSOVLI

tIVSLI

tSLIXI

0.8 VCC

0.2 VCC

0.8 VCC

0.2 VCC

SCK

SOT

SIN

0.7 VCC

0.3 VCC

0.7 VCC

0.3 VCC

tSCYC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB95F582KPFT-G-JNE2 | MICROCONTROLLER, PDSO16 |

| MB95F574KPF-G-JNE2 | MICROCONTROLLER, PDSO8 |

| MB95F582KWQN-G-JNERE1 | MICROCONTROLLER, PQCC32 |

| MB95F562KWQN-G-JNE1 | MICROCONTROLLER, PQCC32 |

| MB95F563HWQN-G-JNERE1 | MICROCONTROLLER, PQCC32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB95F636HP-ES-SH-SNE2 | 制造商:FUJITSU 功能描述:8-bit MCU |

| MB95F636HPMC-ES-SNE2 | 制造商:FUJITSU 功能描述:8-bit FX series microcontroller |

| MB95F636HWQN-ES-SNE1 | 制造商:FUJITSU 功能描述:8-bit MCU |

| MB95F636KP-ES-SH-SNE2 | 制造商:FUJITSU 功能描述:8-bit FX series microcontroller |

| MB95F636KPMC-ES-SNE2 | 制造商:FUJITSU 功能描述:8-bit FX series microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。