- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358131 > MC100LVEL51DG (ON SEMICONDUCTOR) 3.3V ECL Differential Clock D Flip-Flop PDF資料下載

參數(shù)資料

| 型號: | MC100LVEL51DG |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | 鎖存器 |

| 英文描述: | 3.3V ECL Differential Clock D Flip-Flop |

| 中文描述: | 100LVEL SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO8 |

| 封裝: | LEAD FREE, SOIC-8 |

| 文件頁數(shù): | 4/8頁 |

| 文件大?。?/td> | 140K |

| 代理商: | MC100LVEL51DG |

MC100LVEL51

http://onsemi.com

4

Table 6. AC CHARACTERISTICS

V

CC

= 3.3 V; V

EE

= 0.0 V or V

CC

= 0.0 V; V

EE

=

3.3 V (Note 7)

40

°

C

25

°

C

85

°

C

Symbol

Characteristic

Min

Typ

Max

Min

Typ

Max

Min

Typ

Max

Unit

f

max

Maximum Toggle Frequency

2.7

2.8

2.9

GHz

t

PLH

t

PHL

Propagation Delay

to Output

CLK

R

330

340

465

455

510

540

340

350

475

765

520

550

370

390

530

510

550

590

ps

t

S

Setup Time

150

0

150

0

150

0

ps

t

H

Hold Time

200

100

200

100

200

100

ps

t

RR

Reset Recovery

350

200

350

200

350

200

ps

t

PW

Minimum Pulse

Width

CLK

Reset

400

500

400

500

400

500

ps

t

JITTER

Cycle

to

Cycle Jitter

TBD

TBD

TBD

ps

V

PP

Input Swing (Note 8)

150

1000

150

1000

150

1000

mV

t

r

t

f

Output Rise/Fall Times Q

(20%

80%)

120

320

120

320

120

320

ps

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit

board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared

operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit

values are applied individually under normal operating conditions and not valid simultaneously.

7. V

EE

can vary

±

0.3 V.

8. V

PP

(min) is minimum input swing for which AC parameters are guaranteed.

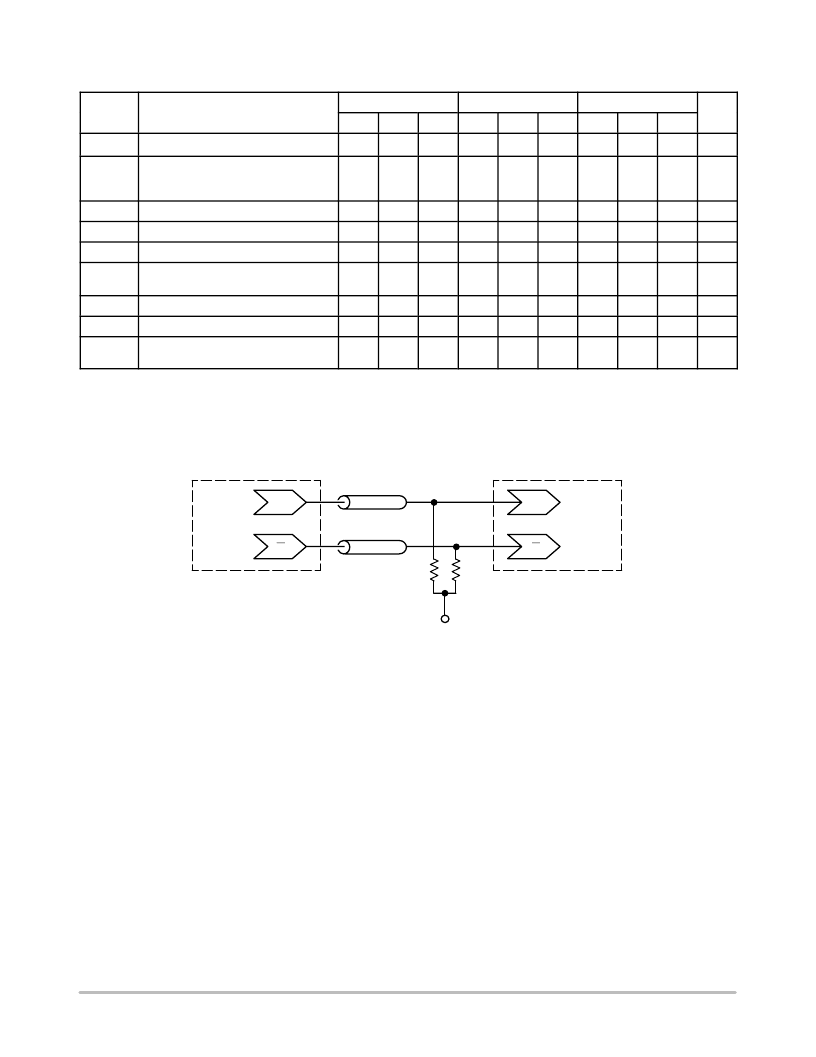

Figure 2. Typical Termination for Output Driver and Device Evaluation

(See Application Note AND8020/D

Termination of ECL Logic Devices.)

Driver

Device

Receiver

Device

Q

D

Q

D

Z

o

= 50

Z

o

= 50

50

50

V

TT

V

TT

= V

CC

3.0 V

相關PDF資料 |

PDF描述 |

|---|---|

| MC100LVEL51DR2G | 3.3V ECL Differential Clock D Flip-Flop |

| MC100LVEL51DT | 3.3V ECL Differential Clock D Flip-Flop |

| MC100LVEL51DTG | 3.3V ECL Differential Clock D Flip-Flop |

| MC100LVEL51DTR2 | 3.3V ECL Differential Clock D Flip-Flop |

| MC100LVEL51DTR2G | 3.3V ECL Differential Clock D Flip-Flop |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MC100LVEL51DR2 | 功能描述:觸發(fā)器 3.3V/5V ECL D-Type RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| MC100LVEL51DR2G | 功能描述:觸發(fā)器 3.3V/5V ECL D-Type w/Diff Clock RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| MC100LVEL51DT | 功能描述:觸發(fā)器 3.3V/5V ECL D-Type RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| MC100LVEL51DTG | 功能描述:觸發(fā)器 3.3V/5V ECL D-Type w/Diff Clock RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| MC100LVEL51DTR2 | 功能描述:觸發(fā)器 3.3V/5V ECL D-Type RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。