- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25639 > MC80C52XXX-16SHXXX (ATMEL CORP) 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 PDF資料下載

參數(shù)資料

| 型號: | MC80C52XXX-16SHXXX |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 |

| 封裝: | 0.600 INCH, SIDE BRAZED, DIP-40 |

| 文件頁數(shù): | 6/80頁 |

| 文件大小: | 5152K |

| 代理商: | MC80C52XXX-16SHXXX |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

198

2466T–AVR–07/10

ATmega16(L)

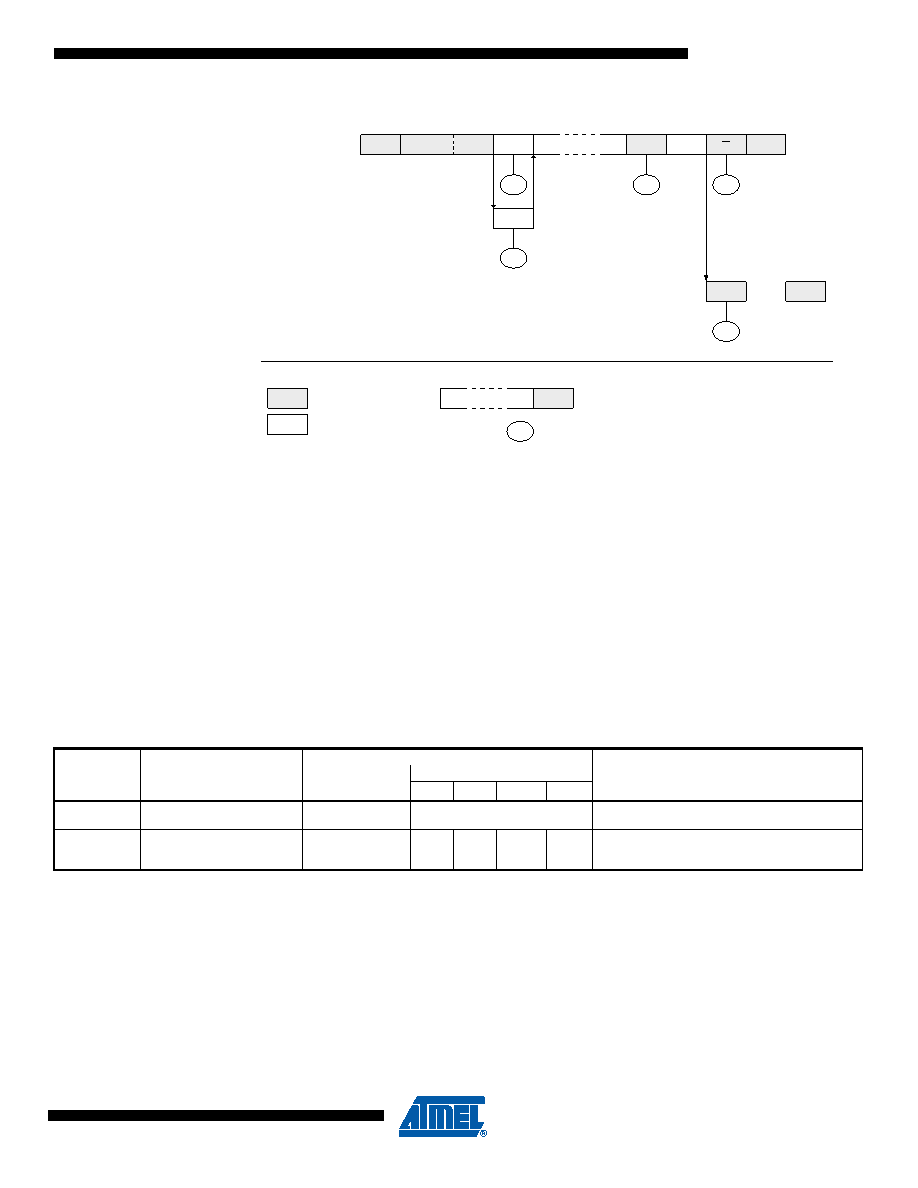

Figure 93. Formats and States in the Slave Transmitter Mode

Miscellaneous States

There are two status codes that do not correspond to a defined TWI state, see Table 78.

Status $F8 indicates that no relevant information is available because the TWINT Flag is not set.

This occurs between other states, and when the TWI is not involved in a serial transfer.

Status $00 indicates that a bus error has occurred during a Two-wire Serial Bus transfer. A bus

error occurs when a START or STOP condition occurs at an illegal position in the format frame.

Examples of such illegal positions are during the serial transfer of an address byte, a data byte,

or an acknowledge bit. When a bus error occurs, TWINT is set. To recover from a bus error, the

TWSTO Flag must set and TWINT must be cleared by writing a logic one to it. This causes the

TWI to enter the not addressed Slave mode and to clear the TWSTO Flag (no other bits in

TWCR are affected). The SDA and SCL lines are released, and no STOP condition is

transmitted.

S

SLA

R

A

DATA

A

$A8

$B8

A

$B0

Reception of the own

slave address and one or

more data bytes

Last data byte transmitted.

Switched to not addressed

slave (TWEA = '0')

Arbitration lost as master

and addressed as slave

n

From master to slave

From slave to master

Any number of data bytes

and their associated acknowledge bits

This number (contained in TWSR) corresponds

to a defined state of the Two-wire Serial Bus. The

prescaler bits are zero or masked to zero

P or S

DATA

$C0

DATA

A

$C8

P or S

All 1's

A

Table 78. Miscellaneous States

Status Code

(TWSR)

Prescaler Bits

are 0

Status of the Two-wire Serial

Bus and Two-wire Serial Inter-

face Hardware

Application Software Response

Next Action Taken by TWI Hardware

To/from TWDR

To TWCR

STA

STO

TWINT

TWEA

$F8

No relevant state information

available; TWINT = “0”

No TWDR action

No TWCR action

Wait or proceed current transfer

$00

Bus error due to an illegal

START or STOP condition

No TWDR action

0

1

X

Only the internal hardware is affected, no STOP condi-

tion is sent on the bus. In all cases, the bus is released

and TWSTO is cleared.

相關PDF資料 |

PDF描述 |

|---|---|

| MD80C52EXXX-20 | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CDIP40 |

| MR80C52CXXX-12SHXXX | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 |

| MC80C52CXXX-12SB | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CDIP40 |

| MQ80C32-25SCD | 8-BIT, 25 MHz, MICROCONTROLLER, CQFP44 |

| MQ80C32E-20SHXXX:D | 8-BIT, 20 MHz, MICROCONTROLLER, CQFP44 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MC80D21000G | 制造商:COR 功能描述:RN |

| MC80F0104 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| MC80F0104B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| MC80F0104D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| MC80F0204 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復。