- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371076 > MC88PL117 (Motorola, Inc.) CMOS PLL CLOCK DRIVER PDF資料下載

參數(shù)資料

| 型號(hào): | MC88PL117 |

| 廠商: | Motorola, Inc. |

| 英文描述: | CMOS PLL CLOCK DRIVER |

| 中文描述: | 的CMOS PLL時(shí)鐘驅(qū)動(dòng)器 |

| 文件頁(yè)數(shù): | 7/11頁(yè) |

| 文件大小: | 139K |

| 代理商: | MC88PL117 |

MC88PL117

TIMING SOLUTIONS

BR1333 — Rev 6

7

MOTOROLA

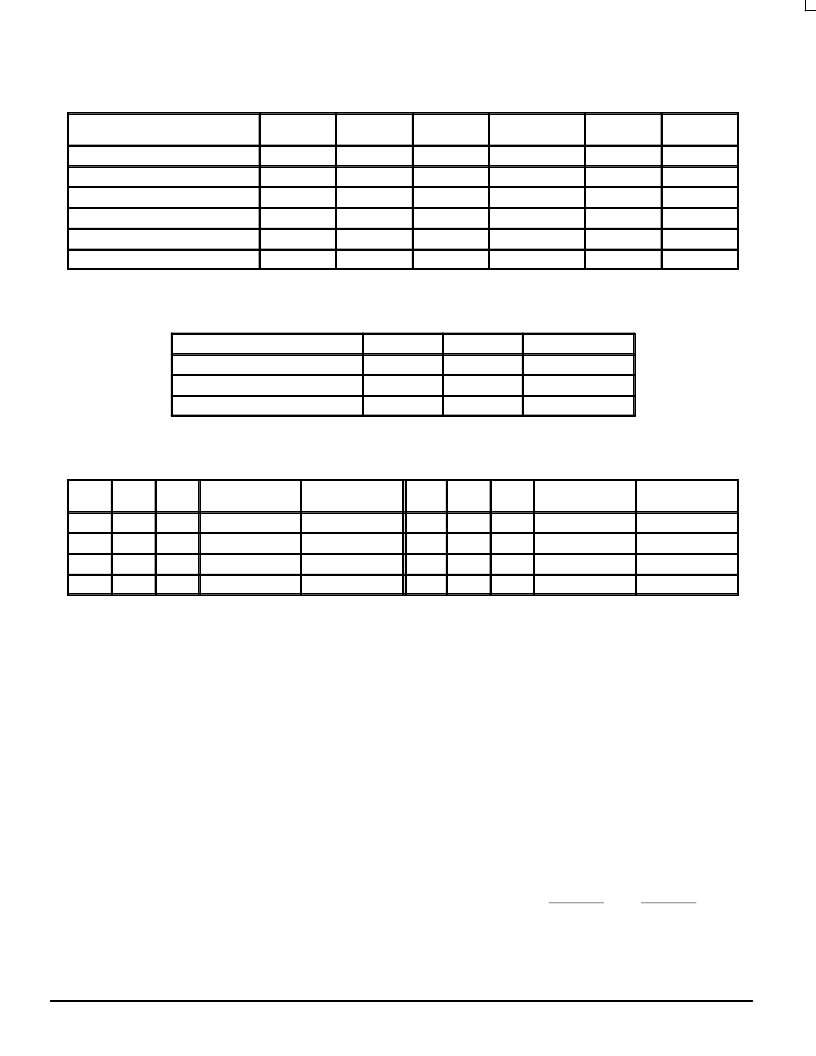

TABLE 1. PROGRAMMABLE OUTPUT CONFIGURATIONS

(Q is system reference frequency)

Output Configuration Number

OPT2

OPT1

OPT0

No of 2X_Q

Outputs

No of Q

Outputs

No of Q/2

Outputs

1

L

L

L

2

12

0

2

L

L

H

2

4

8

3

L

H

L

4

10

0

4

L

H

H

0

14

0

5

H

L

L

0

7

7

6

H

H

H

2

12

0

TABLE 2. PROGRAMMABLE INPUT FREQUENCY MODES

(Multiplication factors)

Input Frequency Mode

MULT1

MULT0

Input Frequency

1

L

L

Q/4

2

L

H

Q/2

3

H

H

Q

TABLE 3. Q

PROGRAMMABLE PHASE INCREMENTS FOR Q AND Q/2 OUTPUTS

2

1

0

Q

Phase

to Q Outputs1

Q

/2 Phase

to Q Outputs2

2

1

0

Q

Phase

to Q Outputs1

Q

/2 Phase

to Q Outputs2

L

L

L

180

°

45

°

H

L

L

180

°

225

°

L

L

H

90

°

90

°

H

L

H

90

°

270

°

L

H

L

0

°

135

°

H

H

L

0

°

315

°

L

H

H

270

°

180

°

H

H

H

270

°

360

°

1. Valid for output configurations 1, 3, 4, 6, 8

2. Valid for output configurations 2, 5, 7

Applications Information

Introduction

The 88PL117 provides the necessary clock frequencies

for the PowerPC 601 and Pentium Microprocessors. With

output frequency capabilities up to 120MHz and the ability to

also generate half and quarter frequency clocks the 88PL117

simplifies the system implementation of a PowerPC 601 or

Pentium Microprocessor. This section will overview the clock

requirements of the PowerPC 601 and Pentium

Microprocessors and apply those to the specification limits of

the 88PL117 to demonstrate compatibility. Although not

exhaustive the intent is to provide a basic set of guidelines on

system implementation. For more cost sensitive applications

which require fewer clocks the designer should refer to the

MC88915TFN133 data sheet for an alternative clock driver

suitable for PowerPC 601 or Pentium Microprocessor based

designs.

Figures 7 and 8 illustrate two common output config–

urations of the 88PL117 which will facilitate POWERPC 601

(MPC601) system designs. Figure 7 would prove beneficial

for high frequency processor designs where the bus clock

would likely run at one fourth the 2X_PCLK input. In this

configuration a 2X_Q output of the 88PL117 can drive the

2X_PCLK of the PowerPC 601 processor while a Q and Q/2

output can drive the PCLK_EN and BCLK_EN inputs

respectively. For designs where the system bus will run at

half the frequency of the 2X_PCLK (same frequency as the

internal processor clock) a larger number of Q outputs would

be required. Figure 8 could be used in this situation with a

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC88PL117FN | CMOS PLL CLOCK DRIVER |

| MC8T13 | DUAL LINE DRIVERS SILICON MONOLITHIC INTEGRATED CIRCUIT |

| MC8T23 | DUAL LINE DRIVERS SILICON MONOLITHIC INTEGRATED CIRCUIT |

| MC8T14 | TRIPLE LINE RECEIVERS WITH HYSTERESIS |

| MC8T24 | TRIPLE LINE RECEIVERS WITH HYSTERESIS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC88PL117FN | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:CMOS PLL CLOCK DRIVER |

| MC890P | 制造商:Motorola Inc 功能描述: |

| MC891L | 制造商:Motorola Inc 功能描述: 制造商:MOTOROLA 功能描述: |

| MC891P | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC893P | 制造商:Motorola Inc 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。