- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359153 > MCF5232CAB80 (飛思卡爾半導(dǎo)體(中國(guó))有限公司) Integrated Microprocessor Hardware Specification PDF資料下載

參數(shù)資料

| 型號(hào): | MCF5232CAB80 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國(guó))有限公司 |

| 英文描述: | Integrated Microprocessor Hardware Specification |

| 中文描述: | 集成的微處理器,硬件規(guī)格 |

| 文件頁(yè)數(shù): | 36/46頁(yè) |

| 文件大小: | 988K |

| 代理商: | MCF5232CAB80 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)

MCF523x Integrated Microprocessor Hardware Specification, Rev. 2

Preliminary Electrical Characteristics

Freescale Semiconductor

36

7.9

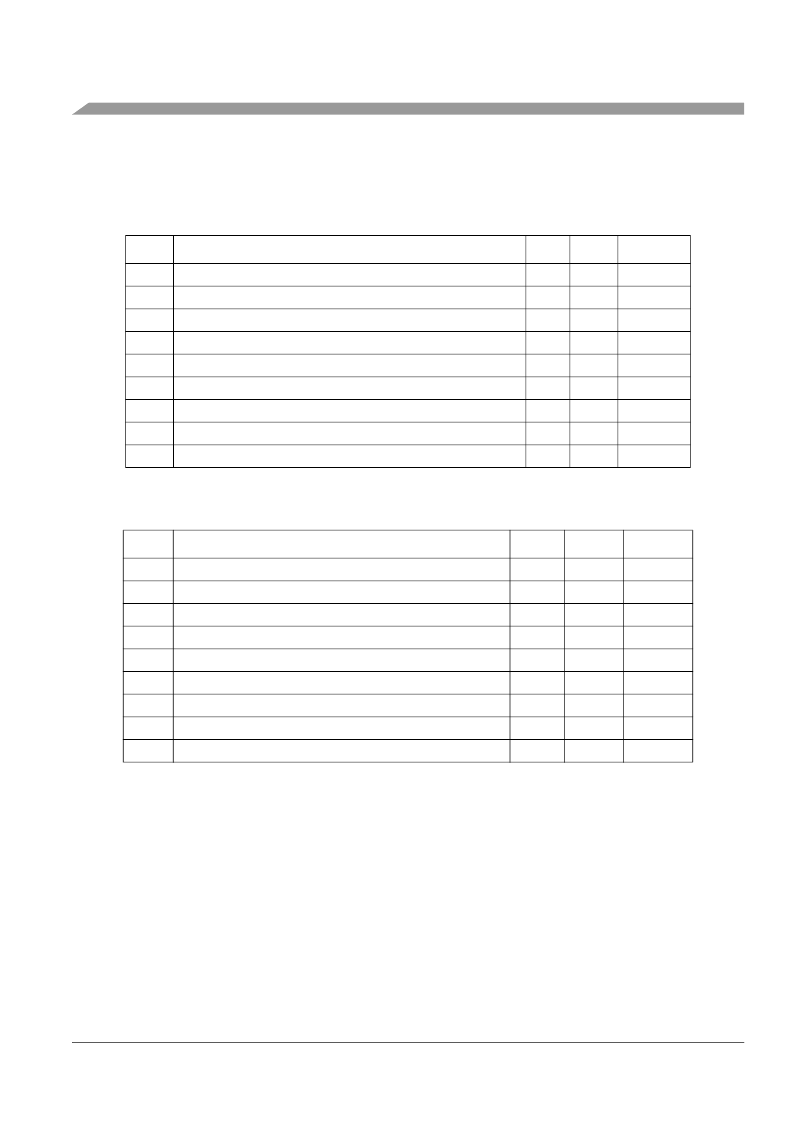

Table 16

lists specifications for the I

2

C input timing parameters shown in

Figure 18

.

Table 16. I

2

C Input Timing Specifications between I2C_SCL and I2C_SDA

I

2

C Input/Output Timing Specifications

Table 17

lists specifications for the I

2

C output timing parameters shown in

Figure 18

.

Table 17. I

2

C Output Timing Specifications between I2C_SCL and I2C_SDA

Figure 18

shows timing for the values in

Table 16

and

Table 17

.

Num

Characteristic

Min

Max

Units

I1

Start condition hold time

2

—

t

cyc

I2

Clock low period

8

—

t

cyc

I3

I2C_SCL/I2C_SDA rise time (V

IL

= 0.5 V to V

IH

= 2.4 V)

—

1

ms

I4

Data hold time

0

—

ns

I5

I2C_SCL/I2C_SDA fall time (V

IH

= 2.4 V to V

IL

= 0.5 V)

—

1

ms

I6

Clock high time

4

—

t

cyc

I7

Data setup time

0

—

ns

I8

Start condition setup time (for repeated start condition only)

2

—

t

cyc

I9

Stop condition setup time

2

—

t

cyc

Num

Characteristic

Min

Max

Units

I1

1

1

Note: Output numbers depend on the value programmed into the IFDR; an IFDR programmed with

the maximum frequency (IFDR = 0x20) results in minimum output timings as shown in

Table 17

. The

I

2

C interface is designed to scale the actual data transition time to move it to the middle of the

I2C_SCL low period. The actual position is affected by the prescale and division values programmed

into the IFDR; however, the numbers given in

Table 17

are minimum values.

Because I2C_SCL and I2C_SDA are open-collector-type outputs, which the processor can only

actively drive low, the time I2C_SCL or I2C_SDA take to reach a high level depends on external

signal capacitance and pull-up resistor values.

Specified at a nominal 50-pF load.

Start condition hold time

6

—

t

cyc

I2

1

Clock low period

10

—

t

cyc

I3

2

2

I2C_SCL/I2C_SDA rise time (V

IL

= 0.5 V to V

IH

= 2.4 V)

—

—

μs

I4

1

Data hold time

7

—

t

cyc

I5

3

3

I2C_SCL/I2C_SDA fall time (V

IH

= 2.4 V to V

IL

= 0.5 V)

—

3

ns

I6

1

Clock high time

10

—

t

cyc

I7

1

Data setup time

2

—

t

cyc

I8

1

Start condition setup time (for repeated start condition only)

20

—

t

cyc

I9

1

Stop condition setup time

10

—

t

cyc

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCF5232 | Integrated Microprocessor Hardware Specification |

| MCF5249 | CodeWarrior Development Studio for ColdFire㈢ Architectures |

| MCF5251_07 | ColdFire㈢ Microprocessor Data Sheet |

| MCF5251 | ColdFire Processor |

| MCF5253 | ColdFire㈢ Microprocessor Data Sheet |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCF5232CVM100 | 功能描述:微處理器 - MPU MCF5232 V2CORE 64KSRAM RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MCF5232CVM100 | 制造商:Freescale Semiconductor 功能描述:Microprocessor IC |

| MCF5232CVM100J | 功能描述:32位微控制器 - MCU V2CORE 64KSRAM RoHS:否 制造商:Texas Instruments 核心:C28x 處理器系列:TMS320F28x 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:90 MHz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:26 KB 片上 ADC:Yes 工作電源電壓:2.97 V to 3.63 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:LQFP-80 安裝風(fēng)格:SMD/SMT |

| MCF5232CVM150 | 功能描述:微處理器 - MPU MCF5232 V2CORE 64KSRAM RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MCF5232CVM150J | 功能描述:32位微控制器 - MCU V2CORE 64KSRAM RoHS:否 制造商:Texas Instruments 核心:C28x 處理器系列:TMS320F28x 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:90 MHz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:26 KB 片上 ADC:Yes 工作電源電壓:2.97 V to 3.63 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:LQFP-80 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。