- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371087 > MCM63P818TQ133 (MOTOROLA INC) 128K x 36 and 256K x 18 Bit Pipelined BurstRAM Synchronous Fast Static RAM PDF資料下載

參數(shù)資料

| 型號(hào): | MCM63P818TQ133 |

| 廠(chǎng)商: | MOTOROLA INC |

| 元件分類(lèi): | DRAM |

| 英文描述: | 128K x 36 and 256K x 18 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

| 中文描述: | 256K X 18 CACHE SRAM, 4 ns, PQFP100 |

| 封裝: | TQFP-100 |

| 文件頁(yè)數(shù): | 22/27頁(yè) |

| 文件大?。?/td> | 328K |

| 代理商: | MCM63P818TQ133 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

MCM63P636

22

MOTOROLA FAST SRAM

TEST ACCESS PORT PINS

TCK — TEST CLOCK (INPUT)

Clocks all TAP events. All inputs are captured on the rising

edge of TCK and all outputs propagate from the falling edge

of TCK.

TMS — TEST MODE SELECT (INPUT)

The TMS input is sampled on the rising edge of TCK. This

is the command input for the TAP controller state machine.

An undriven TMS input will not produce the same result as a

logic one input level (not IEEE 1149.1 compliant).

TDI — TEST DATA IN (INPUT)

The TDI input is sampled on the rising edge of TCK. This is

the input side of the serial registers placed between TDI and

TDO. The register placed between TDI and TDO is deter-

mined by the state of the TAP controller state machine and

the instruction that is currently loaded in the TAP instruction

register (refer to Figure 10, TAP Controller State Diagram).

An undriven TDI pin will not produce the same result as a

logic one input level (not IEEE 1149.1 compliant).

TDO — TEST DATA OUT (OUTPUT)

Output that is active depending on the state of the TAP

state machine (refer to Figure 10, TAP Controller State Dia-

gram). Output changes in response to the falling edge of

TCK. This is the output side of the serial registers placed

between TDI and TDO.

TRST — TAP RESET

The TRST is an asynchronous input that resets the TAP

controller and pre–loads the instruction register with the

IDCODE command. This type of reset does not affect the

operation of the system logic. The reset affects test logic

only.

TEST ACCESS PORT REGISTERS

OVERVIEW

The various TAP registers are selected (one at a time) via

the sequences of ones and zeros input to the TMS pin as the

TCK is strobed. Each of the TAPs registers are serial shift

registers that capture serial input data on the rising edge of

TCK and push serial data out on subsequent falling edge of

TCK. When a register is selected it is “placed” between the

TDI and TDO pins.

INSTRUCTION REGISTER

The instruction register holds the instructions that are

executed by the TAP controller when it is moved into the run

test/idle or the various data register states. The instructions

are three bits long. The register can be loaded when it is

placed between the TDI and TDO pins. The parallel outputs

of the instruction register are automatically preloaded with

the IDCODE instruction when TRST is asserted or whenever

the controller is placed in the test–logic–reset state. The two

least significant bits of the serial instruction register are

loaded with a binary “or” pattern in the capture–IR state.

BYPASS REGISTER

The bypass register is a single bit register that can be

placed between TDI and TDO. It allows serial test data to be

passed through the RAMs TAP to another device in the scan

chain with as little delay as possible.

BOUNDARY SCAN REGISTER

The boundary scan register is identical in length to the

number of active input and I/O connections on the RAM (not

counting the TAP pins). This also includes a number of place

holder locations (always set to a logic 0) reserved for density

upgrade address pins. There are a total of 66 bits in the case

of the x36 device. The boundary scan register, under the

control of the TAP controller, is loaded with the contents of

the RAMs I/O ring when the controller is in capture–DR state

and then is placed between the TDI and TDO pins when the

controller is moved to shift–DR state.

The Bump/Bit Scan Order table describes which device

bump connects to each boundary scan register location. The

first column defines the bit’s position in the boundary scan

register. The shift register bit nearest TDO (i.e., first to be

shifted out) is defined as bit 1. The second column is the

name of the input or I/O at the bump and the third column is

the bump number.

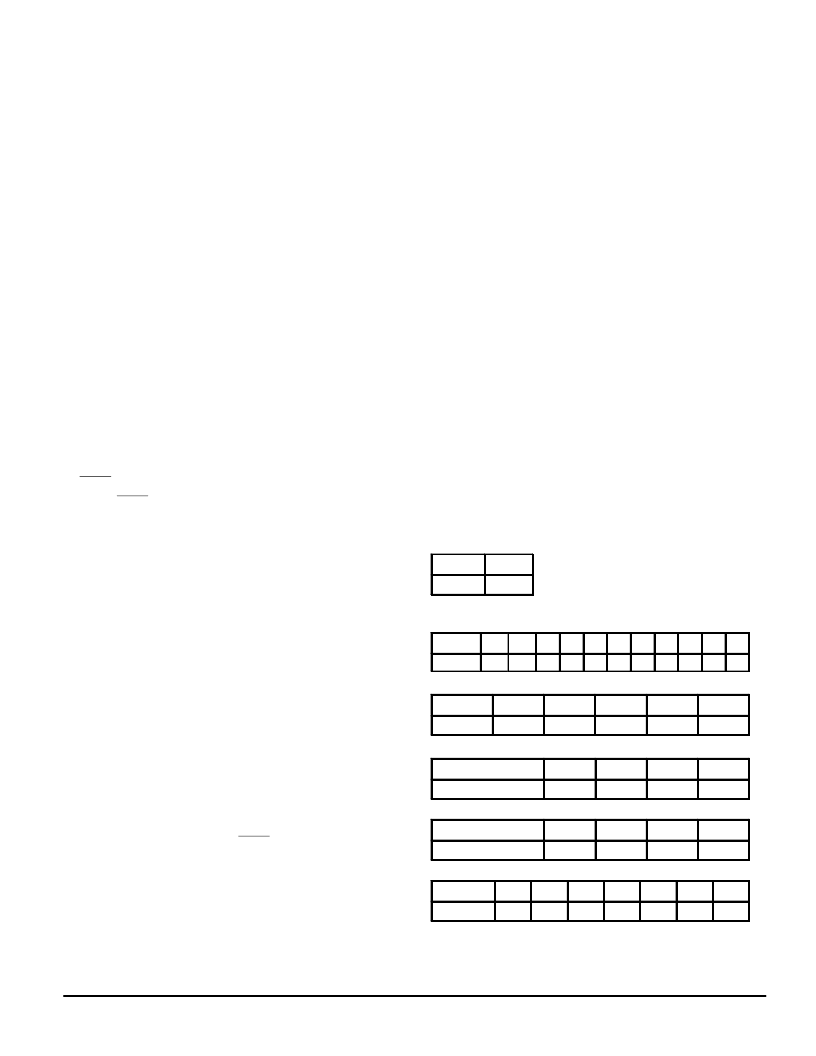

IDENTIFICATION (ID) REGISTER

The ID Register is a 32–bit register that is loaded with a

device and vendor specific 32–bit code when the controller is

put in capture–DR state with the IDCODE command loaded

in the instruction register. The code is loaded from a 32–bit

on–chip ROM. It describes various attributes of the RAM as

indicated below. The register is then placed between the TDI

and TDO pins when the controller is moved into shift–DR

state. Bit 0 in the register is the LSB and the first to reach

TDO when shifting begins.

ID Register Presence Indicator

Bit #

0

Value

1

Motorola JEDEC ID Code (Compressed Format, per

IEEE Standard 1149.1–1990

Bit #

11

10

9

8

7

6

5

4

3

2

1

Value

0

0

0

0

0

0

0

1

1

1

0

Reserved For Future Use

Bit #

16

15

14

13

12

Value

0

0

0

1

0

Device Width

Bit #

20

19

18

17

Value

0

0

1

1

Device Depth

Bit #

24

23

22

21

Value

0

0

1

0

Revision Number

Bit #

31

30

29

28

27

26

25

Value

0

0

0

0

0

0

1

Figure 9. ID Register Bit Meanings

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCM63P818TQ133R | 128K x 36 and 256K x 18 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

| MCM63P818TQ66 | 128K x 36 and 256K x 18 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

| MCM63P818TQ66R | 128K x 36 and 256K x 18 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

| MCM63P818ZP66R | 128K x 36 and 256K x 18 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

| MCM63Z819TQ15R | 128K x 36 and 256K x 18 Bit Flow-Through ZBT RAM Synchronous Fast Static RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCM63P818TQ133R | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:128K x 36 and 256K x 18 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

| MCM63P818TQ66 | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:128K x 36 and 256K x 18 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

| MCM63P818TQ66R | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:128K x 36 and 256K x 18 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

| MCM63P818ZP100 | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:128K x 36 and 256K x 18 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

| MCM63P818ZP100R | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:128K x 36 and 256K x 18 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。