- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9333 > MCP4162T-103E/SN (Microchip Technology)IC POT DGTL SNGL 10K RHEO 8SOIC PDF資料下載

參數(shù)資料

| 型號(hào): | MCP4162T-103E/SN |

| 廠商: | Microchip Technology |

| 文件頁(yè)數(shù): | 36/88頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC POT DGTL SNGL 10K RHEO 8SOIC |

| 標(biāo)準(zhǔn)包裝: | 3,300 |

| 系列: | WiperLock™ |

| 接片: | 257 |

| 電阻(歐姆): | 10k |

| 電路數(shù): | 1 |

| 溫度系數(shù): | 標(biāo)準(zhǔn)值 150 ppm/°C |

| 存儲(chǔ)器類型: | 易失 |

| 接口: | 4 線 SPI(芯片選擇) |

| 電源電壓: | 1.8 V ~ 5.5 V |

| 工作溫度: | -40°C ~ 125°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 8-SOIC(0.154",3.90mm 寬) |

| 供應(yīng)商設(shè)備封裝: | 8-SOICN |

| 包裝: | 帶卷 (TR) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)

2008 Microchip Technology Inc.

DS22059B-page 41

MCP414X/416X/424X/426X

6.1.4

SERIAL CLOCK (SCK)

(SPI FREQUENCY OF OPERATION)

The SPI interface is specified to operate up to 10 MHz.

The actual clock rate depends on the configuration of

the system and the serial command used. Table 6-1

shows the SCK frequency for different configurations.

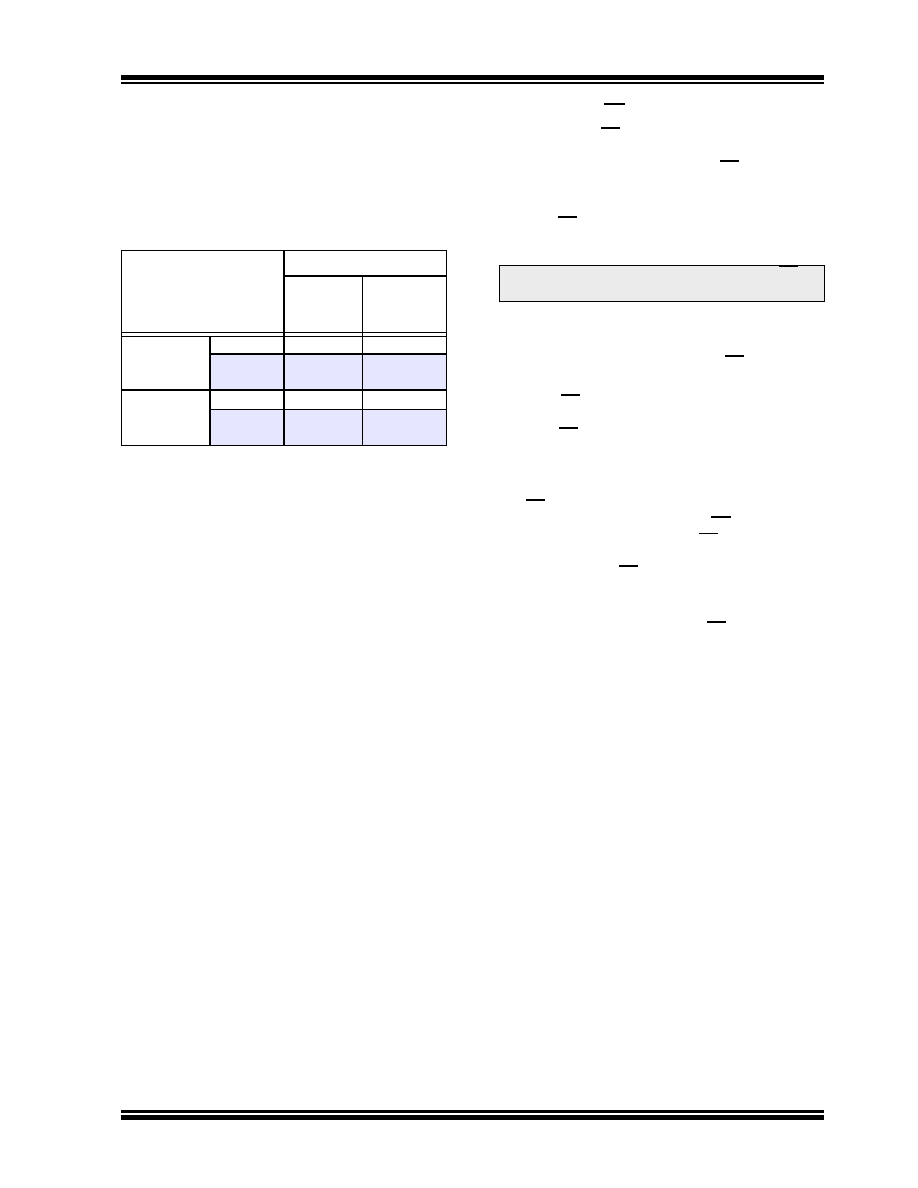

TABLE 6-1:

SCK FREQUENCY

6.1.5

THE CS SIGNAL

The Chip Select (CS) signal is used to select the device

and frame a command sequence. To start a command,

or sequence of commands, the CS signal must

transition from the inactive state (VIH) to an active state

(VIL or VIHH).

After the CS signal has gone active, the SDO pin is

driven and the clock bit counter is reset.

If an error condition occurs for an SPI command, then

the Command byte’s Command Error (CMDERR) bit

(on the SDO pin) will be driven low (VIL). To exit the

error condition, the user must take the CS pin to the VIH

level.

When the CS pin returns to the inactive state (VIH) the

SPI module resets (including the address pointer).

While the CS pin is in the inactive state (VIH), the serial

interface is ignored. This allows the Host Controller to

interface to other SPI devices using the same SDI,

SDO, and SCK signals.

The CS pin has an internal pull-up resistor. The resistor

is disabled when the voltage on the CS pin is at the VIL

level. This means that when the CS pin is not driven,

the internal pull-up resistor will pull this signal to the VIH

level.

When the CS pin is driven low (VIL), the

resistance becomes very large to reduce the device

current consumption.

The high voltage capability of the CS pin allows High

Voltage commands. High Voltage commands allow the

device’s WiperLock Technology and write protect

features to be enabled and disabled.

Memory Type Access

Command

Read

Write,

Increment,

Decrement

Non-Volatile

Memory

SDI, SDO

10 MHz

10 MHz (2, 3)

SDI/SDO

(1)

250 kHz (4) 10 MHz (2, 3)

Volatile

Memory

SDI, SDO

10 MHz

SDI/SDO

(1)

250 kHz (4)

10 MHz

Note 1:

MCP41X1 devices only

2:

Non-Volatile memory does not support

the Increment or Decrement command.

3:

After a Write command, the internal write

cycle must complete before the next SPI

command is received.

4:

This is the maximum clock frequency

without an external pull-up resistor.

Note:

There is a required delay after the CS pin

goes active to the 1st edge of the SCK pin.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VI-2N4-MY-F2 | CONVERTER MOD DC/DC 48V 50W |

| MCP4161T-103E/MF | IC POT DGTL SNGL 10K SPI 8DFN |

| MS3456L20-7S | CONN PLUG 8POS STRAIGHT W/SCKT |

| VE-BN2-IU-F2 | CONVERTER MOD DC/DC 15V 200W |

| VI-2N4-MY-F1 | CONVERTER MOD DC/DC 48V 50W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCP4162T-103I/MF | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:7/8-Bit Single/Dual SPI Digital POT with Non-Volatile Memory |

| MCP4162T-103I/ML | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:7/8-Bit Single/Dual SPI Digital POT with Non-Volatile Memory |

| MCP4162T-103I/MS | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:7/8-Bit Single/Dual SPI Digital POT with Non-Volatile Memory |

| MCP4162T-103I/P | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:7/8-Bit Single/Dual SPI Digital POT with Non-Volatile Memory |

| MCP4162T-103I/SL | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:7/8-Bit Single/Dual SPI Digital POT with Non-Volatile Memory |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。