- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25639 > MD80C32E-20SC (ATMEL CORP) 8-BIT, 20 MHz, MICROCONTROLLER, CDIP40 PDF資料下載

參數(shù)資料

| 型號: | MD80C32E-20SC |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 20 MHz, MICROCONTROLLER, CDIP40 |

| 封裝: | 0.600 INCH, CERAMIC, DIP-40 |

| 文件頁數(shù): | 64/80頁 |

| 文件大小: | 5152K |

| 代理商: | MD80C32E-20SC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁當(dāng)前第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

264

XMEGA A [MANUAL]

8077I–AVR–11/2012

Figure 24-1. Base Address

24.3.2 Address Size

The address size selects how many bits of the address should be compared when generating a chip select. The address

size can be anywhere from 256 bytes to 16MB. If the address space is set to anything larger than 4KB, the base address

must be on a boundary equal to the address space. For example, with 1MB address space for a chip select, the base

address must be on a 1MB, 2MB, etc. boundary.

If the EBI is configured so that the address spaces overlap, the internal memory space will have priority, followed by chip

select 0 (CS0), CS1, CS2, and CS3.

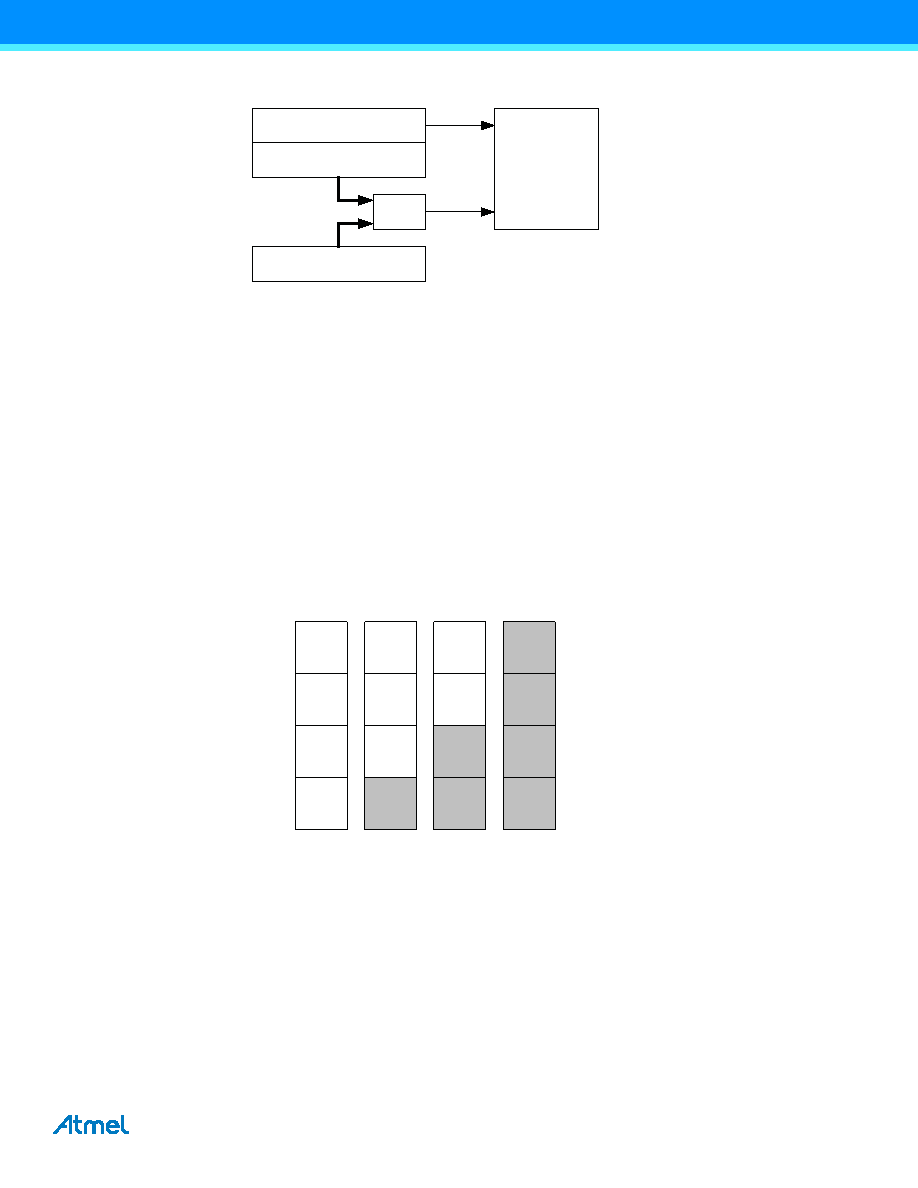

24.3.3 Chip Select as Address Lines

If any chip select lines are unused, these can, in some combinations, be used as address lines. This enables larger

external memory or external CS generation. Each column in Figure 24-2 on page 264 shows enabled chip select lines

(CSn) and the address lines available on unused chip select lines (An). The right-hand column shows that all four CS

lines are used as address lines when only CS3 is enabled.

Figure 24-2. Chip Select and address line combinations

24.4

EBI Clock

The EBI is clocked from the Peripheral 2x (ClkPER2) Clock. This clock can run at the CPU Clock frequency, or at two times

the CPU Clock frequency. This can be used to lower the EBI access time. Refer to “System Clock and Clock Options” on

page 79 for details the Peripheral 2x Clock and how to configure this.

24.5

SRAM Configuration

When used with SRAM, the EBI can be configured with no multiplexing, or it can employ various address multiplexing

modes by using external address latches. When a limited number of pins are available on the device for the EBI, address

latch enable (ALE) signals are used to control the external latches that multiplex address lines from the EBI. The

ADDRESS[23:n]

BASEADDR[23:n]

=

ADDRESS[n-1:0]

A[n-1:0]

D[7:0]

CS

CS3

CS2

CS1

CS0

CS3

CS2

CS1

A16

CS3

CS2

A17

A16

A19

A18

A17

A16

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC80C52XXX-16SHXXX | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 |

| MD80C52EXXX-20 | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CDIP40 |

| MR80C52CXXX-12SHXXX | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 |

| MC80C52CXXX-12SB | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CDIP40 |

| MQ80C32-25SCD | 8-BIT, 25 MHz, MICROCONTROLLER, CQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MD80C51 | 制造商:TEMIC 制造商全稱:TEMIC Semiconductors 功能描述:CMOS 0 to 44 MHz Single-Chip 8 Bit Microcontroller |

| MD80C51BH | 制造商:ROCHESTER 制造商全稱:ROCHESTER 功能描述:CMOS SINGLE - CHIP 8-BIT MICROCOMPUTER 64K program Memory Space |

| MD80C51FB | 制造商:Rochester Electronics LLC 功能描述: |

| MD80C86 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MD80C862 | 制造商:Intel 功能描述:PROCESSOR:MICRO-PROCESSOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。