- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383600 > MH2S64CWZTJ-1539 (Mitsubishi Electric Corporation) Circular Connector; MIL SPEC:MIL-C-26482, Series I, Solder; Body Material:Aluminum; Series:PT00; No. of Contacts:19; Connector Shell Size:14; Connecting Termination:Solder; Circular Shell Style:Wall Mount Receptacle PDF資料下載

參數(shù)資料

| 型號: | MH2S64CWZTJ-1539 |

| 廠商: | Mitsubishi Electric Corporation |

| 元件分類: | 圓形連接器 |

| 英文描述: | Circular Connector; MIL SPEC:MIL-C-26482, Series I, Solder; Body Material:Aluminum; Series:PT00; No. of Contacts:19; Connector Shell Size:14; Connecting Termination:Solder; Circular Shell Style:Wall Mount Receptacle |

| 中文描述: | 134217728位(2097152字,64位)SynchronousDRAM |

| 文件頁數(shù): | 16/45頁 |

| 文件大小: | 691K |

| 代理商: | MH2S64CWZTJ-1539 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

MH2S64CZTJ/CWZTJ-12,-15,-1539

134217728-BIT (2097152-WORD BY 64-BIT)SynchronousDRAM

MITSUBISHI LSIs

( / 45 )

16

MITSUBISHI

ELECTRIC

Oct.28.1996

Preliminary Spec.

Some contents are subject to change without notice.

MIT-DS-0019-0.4

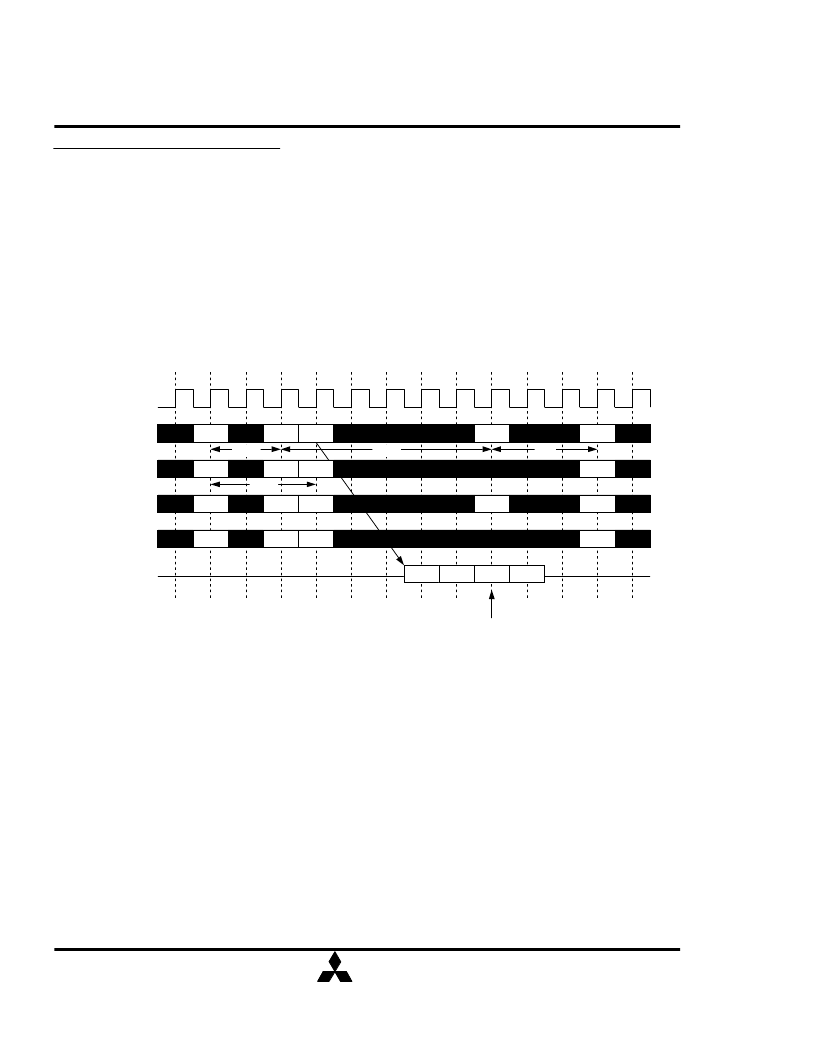

Bank Activation and Precharge All (BL=4, CL=3)

CK

Command

A0-9

A10

BA

DQ

ACT

Xa

Xa

0

READ

Y

0

0

Qa0

Qa1

Qa2

Qa3

ACT

Xb

Xb

1

PRE

tRRD

tRCD

1

ACT

Xb

Xb

1

Precharge all

tRAS

tRP

OPERATION DESCRIPTION

BANK ACTIVATE

The SDRAM has two independent banks. Each bank is activated by the ACT command with

the bank address(BA). A row is indicated by the row address A10-0. The minimum activation

interval between one bank and the other bank is tRRD.

PRECHARGE

The PRE command deactivates indicated by BA. When both banks are active, the precharge

all command(PREA,PRE + A10=H) is available to deactivate them at the same time. After tRP

from the precharge, an ACT command can be issued.

READ

After tRCD from the bank activation, a READ command can be issued. 1st output date is

available after the /CAS Latency from the READ, followed by (BL-1) consecutive date when

the Burst Length is BL. The start address is specified by A8-0, and the address sequence of

burst data is defined by the Burst Type. A READ command may be applied to any active bank,

so the row precharge time(tRP) can be hidden behind continuous output data(in case of BL=8)

by interleaving the dual banks. When A10 is high at a READ command, the

auto-precharge(READA) is performed. Any command (READ, WRITE, PRE, ACT) to the

same bank is inhibited till the internal precharge is complete. The internal precharge start

timing depends on /CAD Latency. The next ACT command can be issued after tRP from the

internal precharge timing.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MH2S64CWXTJ-12 | 134217728-BIT (2097152-WORD BY 64-BIT)SynchronousDRAM |

| MH2S64CWXTJ-15 | 134217728-BIT (2097152-WORD BY 64-BIT)SynchronousDRAM |

| MH2S64CWXTJ-1539 | 134217728-BIT (2097152-WORD BY 64-BIT)SynchronousDRAM |

| MH4V644AXJJ | MS3106B28-18S |

| MH4V64AXJJ-5 | FAST PAGE MODE 268435456-BIT (4194304-WORD BY 64-BIT)DYNAMIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MH2S64CZTJ-12 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:134217728-BIT (2097152-WORD BY 64-BIT)SynchronousDRAM |

| MH2S64CZTJ-15 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:134217728-BIT (2097152-WORD BY 64-BIT)SynchronousDRAM |

| MH2S64CZTJ-1539 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:134217728-BIT (2097152-WORD BY 64-BIT)SynchronousDRAM |

| M-H-3 | 制造商:HRS 制造商全稱:HRS 功能描述:RFCO-AXIAL CONNECTORS |

| MH3012-02 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MH - MODULAR SERIES |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。