- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371107 > MH32V725BST-6 (Mitsubishi Electric Corporation) HYPER PAGE MODE 2415919104 - BIT ( 33554432 - WORD BY 72 - BIT ) DYNAMIC RAM PDF資料下載

參數(shù)資料

| 型號(hào): | MH32V725BST-6 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | HYPER PAGE MODE 2415919104 - BIT ( 33554432 - WORD BY 72 - BIT ) DYNAMIC RAM |

| 中文描述: | 超頁(yè)模式2415919104 -位(33554432 - Word的72 -位)動(dòng)態(tài)隨機(jī)存儲(chǔ)器 |

| 文件頁(yè)數(shù): | 1/22頁(yè) |

| 文件大小: | 135K |

| 代理商: | MH32V725BST-6 |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)

MITSUBISHI LSIs

MH32V725BST -5, -6

Preliminary Spec.

MITSUBISHI

ELECTRIC

27/Jul./1998

HYPER PAGE MODE 2415919104 - BIT ( 33554432 - WORD BY 72 - BIT ) DYNAMIC RAM

MIT - DS - 0237-0.0

DESCRIPTION

The MH32V725BST is 33554432-word x 72-bit dynamic

ram stacked structural module. This consist of thirty-six

industry standard 16M x 4 dynamic RAMs in TSOP and

two industry standard input buffer in TSSOP.

The mounting of TSOP on a card edge dual in-line package

provides any application where high densities and large of

quantities memory are required.

This is a socket-type memory module ,suitable for easy

interchange or addition of module.

FEATURES

MH32V725BST-5

MH32V725BST-6

Type name

/RAS

access

time

(max.ns)

/CAS

access

time

(max.ns)

Address

access

time

(max.ns)

/OE

access

time

(max.ns)

Cycle

Power

time

(min.ns)

dissipation

(typ.W)

50

60

19

21

30

35

19

21

84

104

Utilizes industry standard 16M x 4 RAMs SOJ and industry

standard input buffer in TSSOP

168-pin (84-pin dual dual in-line package)

Single 3.3V(± 0.3V) supply operation

Low stand-by power dissipation . . . . . . . . . . 135.7mW(Max)

Low operation power dissipation

MH32V725BST -5 . . . . . . . . . . . . . . . . . . 14.96W(Max)

MH32V725BST -6 . . . . . . . . . . . . . . . . . . 13.66W(Max)

All input are directly LVTTL compatible

All output are three-state and directry LVTTL compatible

Includes(0.22 uF x 38) decoupling capacitors

4096 refresh cycle every 64ms (CBR Ref)

8192 refresh cycle every 64ms (RAS Only Ref,Normal R/W)

Hyper-page mpde,Read-modify-write,/CAS before /RAS refresh,

Hidden refresh capabilities

JEDEC standard pin configration & Buffered PD pin

Buffered input except /RAS and DQ

Gold plating contact pads

APPLICATION

Main memory unit for computers , Microcomputer memory

PD&ID TABLE

PD1 PD2 PD3 PD4 PD5 PD6 PD7 PD8 ID0

1

0

0

0

1

1

0

0

0

1

ID1

0

0

- 6

- 5

1 = NC , 0 = drive to VOL

PD pin . . . buffered. When /PDE is low, PD information can be read

ID pin . . . non-buffered

0

1

0

1

0

0

0

0

12.8

11

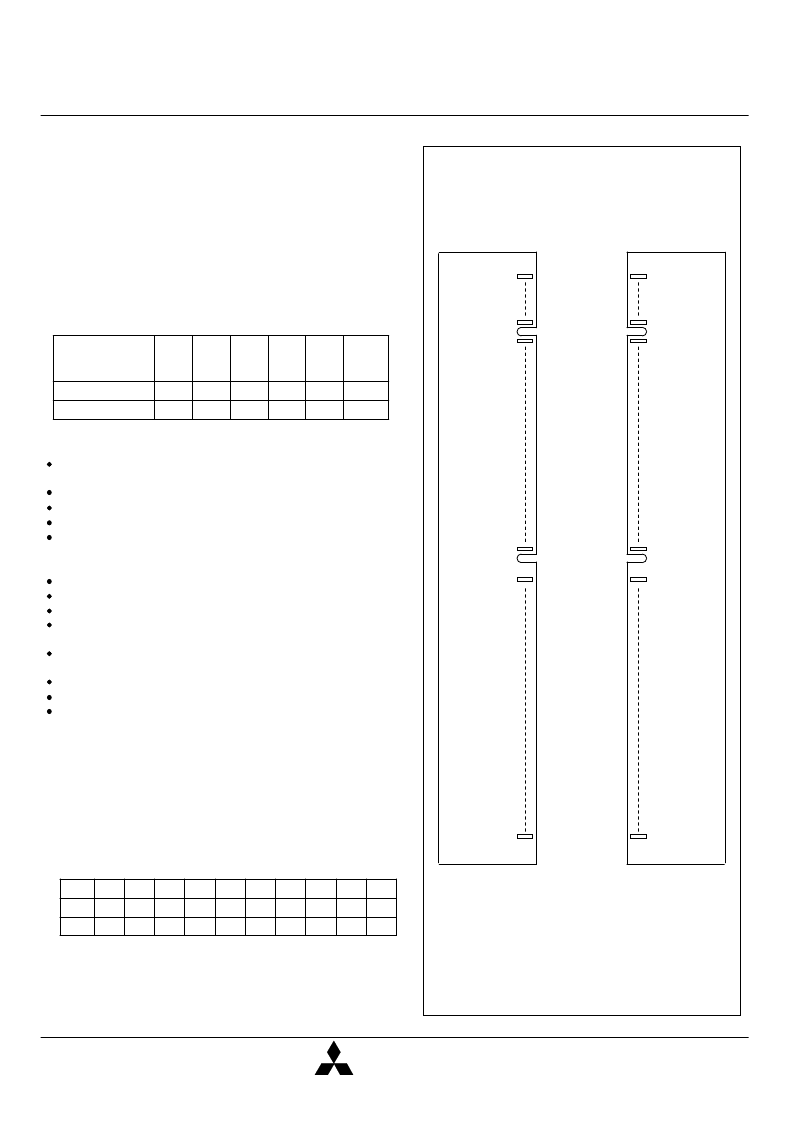

PIN CONFIGURATION

1pin

10pin

11pin

40pin

41pin

84pin

85pin

94pin

95pin

124pin

125pin

168pin

FRONT SIDE

BACK SIDE

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MH4M365CNXJ-7 | HYPER PAGE MODE 150994944-BIT ( 4194304-WORD BY 36-BIT ) DYNAMIC RAM |

| MH4M365CNXJ-5 | HYPER PAGE MODE 150994944-BIT ( 4194304-WORD BY 36-BIT ) DYNAMIC RAM |

| MH4M365CXJ-5 | HYPER PAGE MODE 150994944-BIT ( 4194304-WORD BY 36-BIT ) DYNAMIC RAM |

| MH4M365CXJ-6 | HYPER PAGE MODE 150994944-BIT ( 4194304-WORD BY 36-BIT ) DYNAMIC RAM |

| MH4M365CNXJ-6 | HYPER PAGE MODE 150994944-BIT ( 4194304-WORD BY 36-BIT ) DYNAMIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MH32WP | 制造商:Square D by Schneider Electric 功能描述:PANELBOARD ENCL/BOX TYPE 3R/12 32H 20W |

| MH33 | 制造商:APEM 功能描述: |

| MH33FAD | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:8 pin DIP, 3.3 or 5.0 Volt, HCMOS/TTL Clock Oscillator |

| MH33FAD-R | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:8 pin DIP, 3.3 or 5.0 Volt, HCMOS/TTL Clock Oscillator |

| MH33FAG | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:8 pin DIP, 3.3 or 5.0 Volt, HCMOS/TTL Clock Oscillator |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。