- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45328 > MK1492-02RTRLF (INTEGRATED DEVICE TECHNOLOGY INC) 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 PDF資料下載

參數(shù)資料

| 型號: | MK1492-02RTRLF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| 封裝: | 0.150 INCH, SSOP-28 |

| 文件頁數(shù): | 7/7頁 |

| 文件大?。?/td> | 70K |

| 代理商: | MK1492-02RTRLF |

MK1492-02

Intel Mobile/SDRAM Clock Source

MDS1492-02E

7

Revision 2028

Printed 2/2/98

MicroClock Division of ICS1271 Parkmoor Ave.San JoseCA95126(408)295-9800tel(408)295-9818fax

PRELIMINARY INFORMATION

ICRO

CLOCK

While the information presented herein has been checked for both accuracy and reliability, MicroClock Incorporated assumes no responsibility for either its use or for the

infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in

normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements

are not recommended without additional processing by MicroClock. MicroClock reserves the right to change any circuitry or specifications without notice. MicroClock does not

authorize or warrant any MicroClock product for use in life support devices or critical medical instruments.

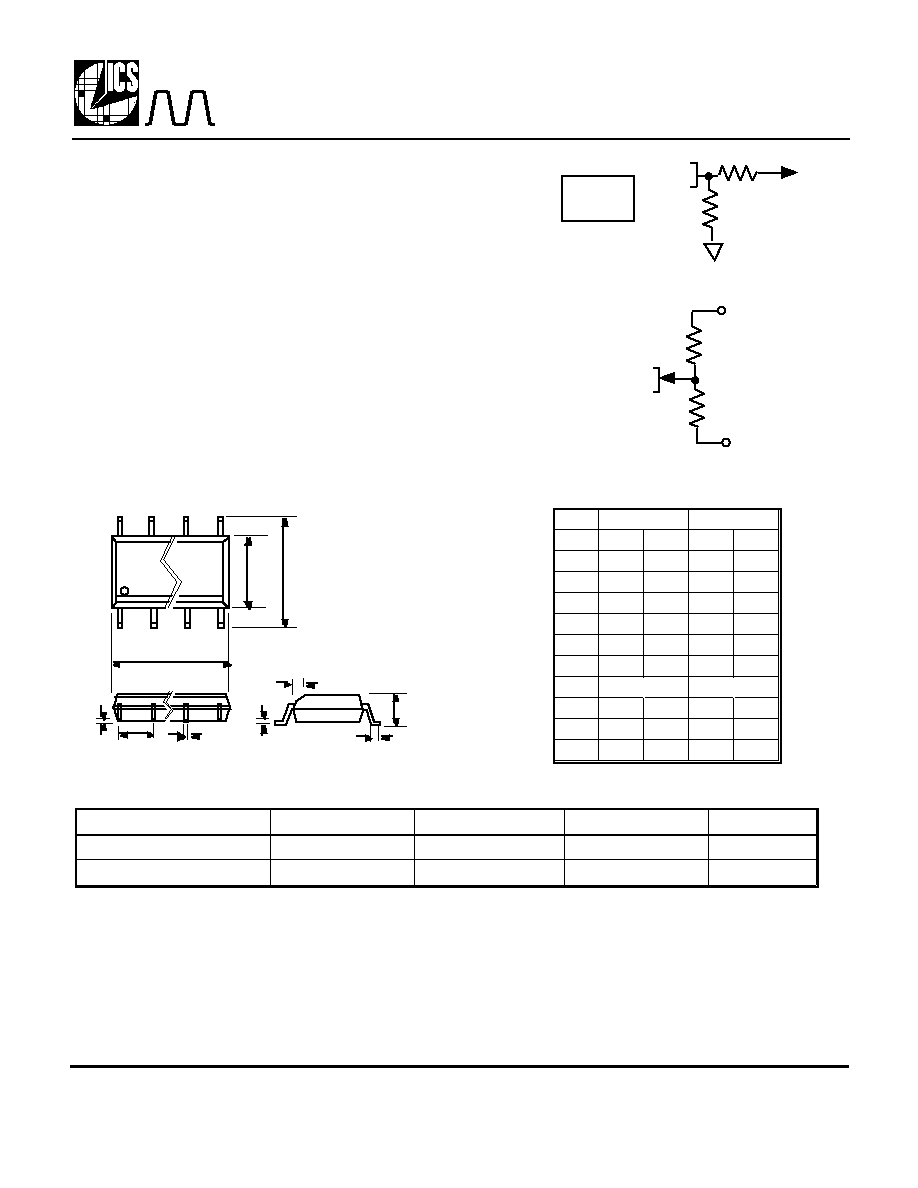

b

D

E

H

e

Q

c

A

h x 45°

Package Outline and Package Dimensions

Ordering Information

Pentium is a trademark of Intel Corporation

28 pin SSOP

Inches

Millimeters

Symbol

Min

Max

Min

Max

A

0.061

0.068

1.55

1.73

b

0.008

0.012

0.203

0.305

c

0.007

0.010

0.190

0.254

D

0.385

0.400

9.780 10.160

E

0.150

0.160

3.810

4.064

H

0.230

0.245

5.840

6.223

e

.025 BSC

0.635 BSC

h

0.016

0.410

L

0.016

0.035

0.406

0.889

Q

0.004

0.01

0.127

0.254

Part/Order Number

Marking

Low EMI Feature

Package

Temperature

MK1492-02R

Yes

28 pin SSOP

0-70°C

MK1492-02RTR

MK1492-02R

Yes

Add Tape & Reel

-

I/O Structure

The MK1492 provides more functionality in a 28 pin package by using a

unique I/O technique. The device checks the status of all I/O pins during

power-up. This status (pulled high or low) then determines the frequency

selections and power down modes (see the tables on page 2). Within 10ms

after power up, the inputs change to outputs and the clocks start up. In the

diagrams to the right, the 33

resistors are the normal output

termination resistors. The 10k

resistor pulls low to generate a logic

zero. Internal pull-up resistors (approx. 100k

) are present on DS, SEL0,

FS, LE, CPUS#, PCISTP#, and CSSS. Internal resistors on PEN, SEL1,

and OE pull to a mid-level (M).

The CPUS# input should be connected as shown to implement the 0, M,

and 1 selections per the Power Down Control Table on page 2. Contact

MicroClock for suggested connections of PCISTP# if the PLL STOP

mode will be used.

to load

I/O

CPUS#

For select

= 0 (low)

10k

33

10k

CPU_STOP#

Don’t stuff for

“1” selection

10k

PWR_DOWN#

Signals from

North Bridge

L

相關PDF資料 |

PDF描述 |

|---|---|

| MK1492-02RLF | 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| MK1492-04RTRLF | 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| MK1492-04RTR | 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| MK1492-04R | 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| MK1493-01G | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MK1492-03R | 功能描述:時鐘驅動器及分配 INTEL MOBILE/SDRAM CLOCK SOURCE RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| MK1492-03RTR | 功能描述:IC CLK SRC MOBILE/SDRAM 28-QSOP RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標準包裝:28 系列:- 類型:時鐘/頻率發(fā)生器 PLL:是 主要目的:Intel CPU 服務器 輸入:時鐘 輸出:LVCMOS 電路數(shù):1 比率 - 輸入:輸出:3:22 差分 - 輸入:輸出:無/是 頻率 - 最大:400MHz 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:64-TFSOP (0.240",6.10mm 寬) 供應商設備封裝:64-TSSOP 包裝:管件 |

| MK1493-01 | 制造商:ICS 制造商全稱:ICS 功能描述:PCI Clock Generator |

| MK1493-01G | 制造商:ICS 制造商全稱:ICS 功能描述:PCI Clock Generator |

| MK1493-01GTR | 制造商:ICS 制造商全稱:ICS 功能描述:PCI Clock Generator |

發(fā)布緊急采購,3分鐘左右您將得到回復。