- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25627 > MK74CB178R CB SERIES, LOW SKEW CLOCK DRIVER, 7 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 PDF資料下載

參數(shù)資料

| 型號: | MK74CB178R |

| 元件分類: | 時鐘及定時 |

| 英文描述: | CB SERIES, LOW SKEW CLOCK DRIVER, 7 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 封裝: | 0.150 INCH, SSOP-28 |

| 文件頁數(shù): | 3/4頁 |

| 文件大小: | 45K |

| 代理商: | MK74CB178R |

MK74CB178

Early Buffalo Clock Driver

MDS74CB178B

3

Revision 4265

Printed 7/23/97

MicroClock Division of ICS1271 Parkmoor Ave.San JoseCA95126(408)295-9800tel(408)295-9818fax

ICRO

CLOCK

Parameter

Conditions

Minimum

Typical

Maximum

Units

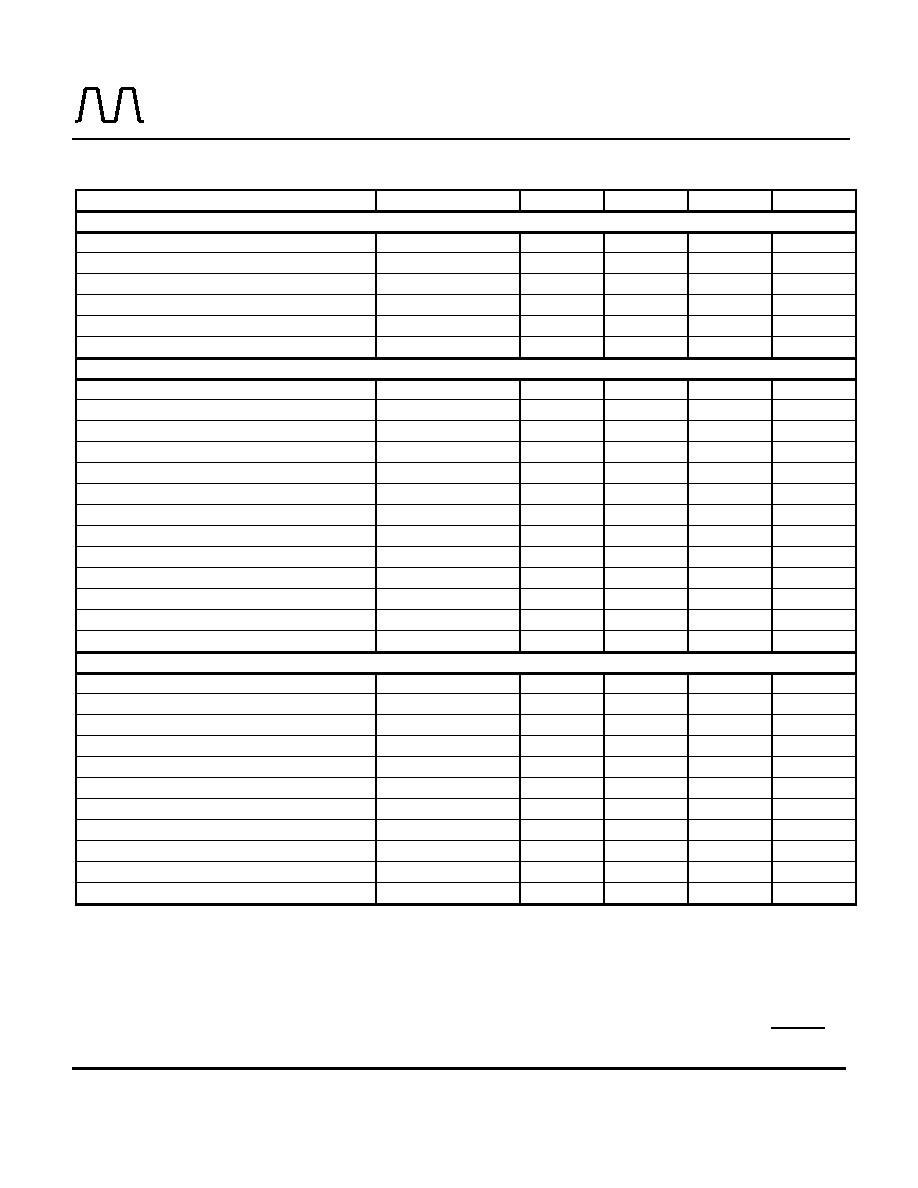

ABSOLUTE MAXIMUM RATINGS (Note 1)

Supply Voltage, VDD

Referenced to GND

7

V

Inputs

Referenced to GND

0.5

VDD+0.5

V

Clock Outputs

Referenced to GND

0.5

VDD+0.5

V

Ambient Operating Temperature

0

70

°C

Soldering Temperature

Max of 20 seconds

260

°C

Storage Temperature

-65

150

°C

DC CHARACTERISTICS (VDD = 5V unless noted)

Operating Voltage, VDD

3.0

5.5

V

Input High Voltage, VIH (INA, INB, INC pins)

VDD-1

VDD/2

V

Input Low Voltage, VIL (INA, INB, INC pins)

VDD/2

1

V

Input High Voltage, VIH (OEA pin)

2.0

V

Input Low Voltage, VIL (OEA pin)

0.8

V

Output High Voltage, 3.3V and 5V

IOH=-8mA

VDD-0.4

V

Output High Voltage, 3.3V and 5V

IOH=-12mA

2.4

V

Output Low Voltage, 3.3V and 5V

IOL=12mA

0.8

V

Operating Supply Current, IDD, at 66.6MHz

No Load

20

mA

Short Circuit Current

Each output

±70

mA

Short Circuit Current at 3.3V

Each output

±35

mA

On-Chip Pull-up Resistor

OEA pin

250

k

Input Capacitance

7

pF

AC CHARACTERISTICS (VDD = 5V unless noted)

Input Clock Frequency

67

MHz

Propagation Delay with load=10pF

2

3.5

5

ns

Propagation Delay with load=10pF

At VDD=3.3V

2.5

4.5

6.5

ns

Output Clock Rise Time, 3.3V and 5V

0.8 to 2.0V

1.5

ns

Output Clock Fall Time, 3.3V and 5V

2.0 to 0.8V

1.5

ns

Output Clock Rising Edge Skew, 3.3V and 5V

At VDD/2. Note 2

50

250

ps

Output Clock A to B to C Skew, 3.3V and 5V

At VDD/2. Note 3

100

500

ps

Output Enable Time, OEA high to output on

5

20

ns

Output Disable Time, OEA low to tri-state

65

100

ns

Maximum load per output pin

At 66.66 MHz

25

pF

Maximum load per side of 8 outputs

Note 4

120

pF

Electrical Specifications

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings could cause permanent damage to the device. Prolonged exposure

to levels above the operating limits but below the Absolute Maximums may affect device reliability.

2. Between any two A outputs, or any two B outputs, with equal loading.

3. Between any clock A or clock B or clock C outputs with inputs connected. With VDDA=VDDBC and equal loading. Combined

with the 250ps uncertainty of MicroClock’s Clock Synthesizers, this adds to a 750ps total. The new PCI specifications allow a 2ns

difference between PCI and CPU clocks.

4. This is the load per sum of all A outputs, or all B+C outputs, at 66.66MHz. The formula for per side load is CL (F) =

8 x 10-3

f (in Hz)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MK74CB218RTR | CB SERIES, LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| ML65F16244CT | QUAD 4-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| ML65F16245CR | DUAL 8-BIT TRANSCEIVER, TRUE OUTPUT, PDSO48 |

| ML67Q5260-NNNHB | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA63 |

| MM54C165J | CMOS SERIES, 8-BIT RIGHT PARALLEL IN SERIAL OUT SHIFT REGISTER, COMPLEMENTARY OUTPUT, CDIP16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MK74CB214 | 制造商:ICS 制造商全稱:ICS 功能描述:Dual 1 to 7 Buffalo⑩ Clock Driver |

| MK74CB214R | 制造商:ICS 制造商全稱:ICS 功能描述:Dual 1 to 7 Buffalo⑩ Clock Driver |

| MK74CB214RTR | 制造商:ICS 制造商全稱:ICS 功能描述:Dual 1 to 7 Buffalo⑩ Clock Driver |

| MK74CB217 | 制造商:ICS 制造商全稱:ICS 功能描述:Dual 1 to 8 Buffalo⑩ Clock Driver |

| MK74CB217R | 制造商:ICS 制造商全稱:ICS 功能描述:Dual 1 to 8 Buffalo⑩ Clock Driver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。