- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377983 > MM74C574MTC (FAIRCHILD SEMICONDUCTOR CORP) 3-STATE Octal D-Type Edge-Triggered Flip-Flop PDF資料下載

參數(shù)資料

| 型號: | MM74C574MTC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | 3-STATE Octal D-Type Edge-Triggered Flip-Flop |

| 中文描述: | CMOS SERIES, 8-BIT DRIVER, TRUE OUTPUT, PDSO20 |

| 封裝: | 4.40 MM, MO-153, TSSOP-20 |

| 文件頁數(shù): | 3/8頁 |

| 文件大小: | 102K |

| 代理商: | MM74C574MTC |

3

www.fairchildsemi.com

M

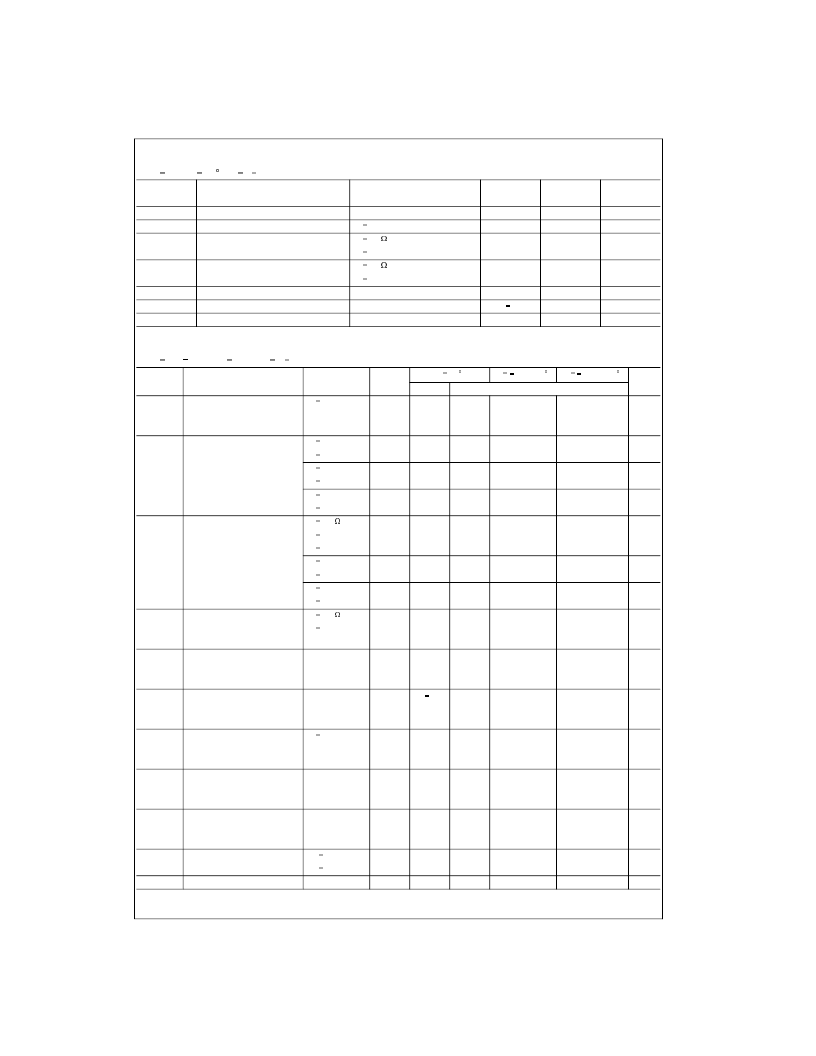

AC Electrical Characteristics

V

CC

5V, T

A

25

q

C, t

r

t

f

6 ns

AC Electrical Characteristics

V

CC

2.0 6.0V, C

L

50 pF, t

r

t

f

6 ns (unless otherwise specified)

Symbol

Parameter

Conditions

Typ

Guaranteed

Limit

33

27

28

Units

f

MAX

t

PHL

, t

PLH

t

PZH

, t

PZL

Maximum Operating Frequency

Maximum Propagation Delay, Clock to Q

Maximum Output Enable Time

60

17

19

MHz

ns

ns

C

L

45 pF

R

L

1 k

:

C

L

45 pF

R

L

1 k

:

C

L

5 pF

t

PHZ

, t

PLZ

Maximum Output Disable Time

14

25

ns

t

S

t

H

t

W

Minimum Setup Time, Data to Clock

Minimum Hold Time, Clock to Data

Minimum Pulse Clock Width

10

3

8

12

5

15

ns

ns

ns

Symbol

Parameter

Conditions

V

CC

T

A

25

q

C

Typ

T

A

40 to 85

q

C T

A

55 to 125

q

C

Guaranteed Limits

28

Units

f

MAX

Maximum Operating Frequency

C

L

50 pF

2.0V

33

23

MHz

4.5V

6.0V

2.0V

30

35

30

24

28

38

20

23

45

t

PHL

, t

PLH

Maximum Propagation

C

L

50 pF

C

L

150 pF

C

L

50 pF

C

L

150 pF

C

L

50 pF

C

L

150 pF

R

L

1 k

:

C

L

50 pF

C

L

150 pF

C

L

50 pF

C

L

150 pF

C

L

50 pF

C

L

150 pF

R

L

1 k

:

C

L

50 pF

18

ns

Delay, Clock to Q

2.0V

4.5V

4.5V

51

13

19

155

23

31

194

29

47

233

35

47

ns

6.0V

6.0V

12

18

20

27

25

34

30

41

ns

t

PZH

, t

PZL

Maximum Output Enable

Time

2.0V

2.0V

4.5V

22

59

14

30

180

28

38

225

35

45

270

42

ns

ns

4.5V

6.0V

6.0V

20

12

18

36

24

31

45

30

39

54

36

47

ns

t

PHZ

, t

PLZ

Maximum Output Disable Time

2.0V

4.5V

6.0V

15

12

10

30

25

21

38

31

27

45

38

32

ns

t

S

Minimum Setup Time

Data to Clock

2.0V

4.5V

6.0V

6

12

20

17

15

25

21

18

30

25

ns

t

H

Minimum Hold Time

Clock to Data

2.0V

4.5V

6.0V

1

5

0

0

6

0

0

8

0

0

ns

t

THL

, t

TLH

Maximum Output Rise

and Fall Time

C

L

50 pF

2.0V

4.5V

6.0V

6

7

6

12

12

10

15

15

13

18

18

15

ns

t

W

Minimum Clock Pulse Width

2.0V

4.5V

6.0V

30

9

8

15

16

14

20

20

18

24

24

20

ns

t

r

,t

f

Maximum Clock Input Rise

and Fall Time

2.0V

4.5V

6.0V

1000

500

400

1000

500

400

1000

500

400

ns

C

PD

Power Dissipation Capacitance

(Note 5) (per latch)

Maximum Input Capacitance

OC

V

CC

OC

GND

5

pF

58

5

C

IN

10

10

10

pF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MM74C574N | 3-STATE Octal D-Type Edge-Triggered Flip-Flop |

| MM74C574SJ | 3-STATE Octal D-Type Edge-Triggered Flip-Flop |

| MM74C574WM | 3-STATE Octal D-Type Edge-Triggered Flip-Flop |

| MM74HC574 | 1.5 A, 520 kHz Low Voltage Buck Regulators with Synchronization Capability; Package: DFN18 6x5, 0.5p; No of Pins: 18; Container: Tape and Reel; Qty per Container: 2500 |

| MM74HC574MTCX | 3-STATE Octal D-Type Edge-Triggered Flip-Flop |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MM74C574N | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:3-STATE Octal D-Type Edge-Triggered Flip-Flop |

| MM74C574SJ | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:3-STATE Octal D-Type Edge-Triggered Flip-Flop |

| MM74C574WM | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:3-STATE Octal D-Type Edge-Triggered Flip-Flop |

| MM74C73 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Dual J-K Flip-Flops with Clear and Preset |

| MM74C73_04 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Dual J-K Flip-Flops with Clear and Preset |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。