- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371134 > MPC2003SG60 (MOTOROLA INC) 256KB and 512KB BurstRAM Secondary Cache Module for PowerPC - Based Systems PDF資料下載

參數(shù)資料

| 型號(hào): | MPC2003SG60 |

| 廠商: | MOTOROLA INC |

| 元件分類: | SRAM |

| 英文描述: | 256KB and 512KB BurstRAM Secondary Cache Module for PowerPC - Based Systems |

| 中文描述: | 128K X 36 CACHE SRAM MODULE, 11 ns, DMA136 |

| 封裝: | DIMM-136 |

| 文件頁(yè)數(shù): | 5/14頁(yè) |

| 文件大?。?/td> | 234K |

| 代理商: | MPC2003SG60 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

MPC2002

MPC2003

5

MOTOROLA FAST SRAM

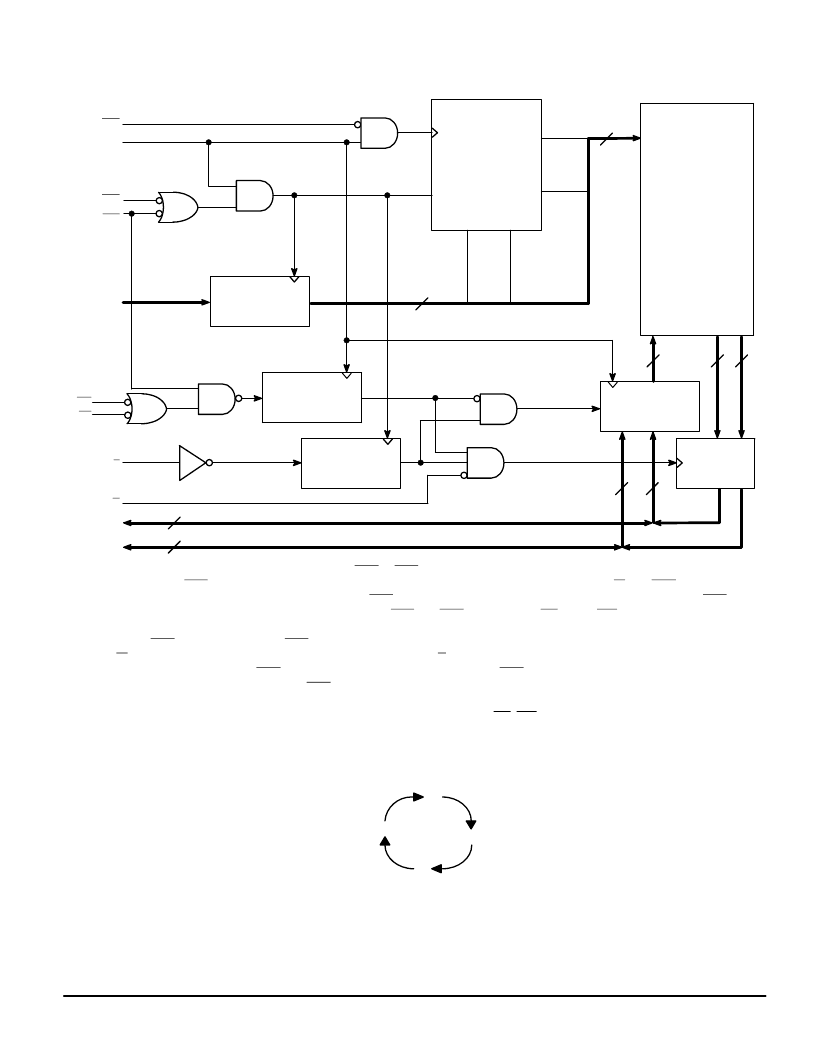

BLOCK DIAGRAM

(See Note)

EXTERNAL

ADDRESS

16

9

9

18

16

A15 – A2

DQ0 – DQ8

INTERNAL

ADDRESS

64K x 18

MEMORY

ARRAY

ADDRESS

REGISTERS

WRITE

REGISTER

ENABLE

REGISTER

DATA–IN

REGISTERS

OUTPUT

BUFFER

BAA

K

TSP

TSC

A15 – A0

UW

LW

E

G

9

DQ9 – DQ17

9

9

9

A0

′

A1

′

A1

LOAD

D1

BINARY

COUNTER

D0

Q1

Q0

BURST LOGIC

A0

NOTE:

All registers are positive–edge triggered. The TSC or TSP signals control the duration of the burst and the start of the next

burst. When TSP is sampled low, any ongoing burst is interrupted and a read (independent of W and TSC) is performed

using the new external address. Alternatively, a TSP–initiated two cycle WRITE can be performed by asserting TSP and

a valid address on the first cycle, then negating both TSP and TSC and asserting LW and/or UW with valid data on the se-

cond cycle (see Single Write Cycle in WRITE CYCLES timing diagram).

When TSC is sampled low (and TSP is sampled high), any ongoing burst is interrupted and a read or write (dependent on

W) is performed using the new external address. Chip enable (E) is sampled only when a new base address is loaded. After

the first cycle of the burst, BAA controls subsequent burst cycles. When BAA is sampled low, the internal address is ad-

vanced prior to the operation. When BAA is sampled high, the internal address is not advanced, thus inserting a wait state

into the burst sequence accesses. Upon completion of a burst, the address will wrap around to its initial state. See

BURST

SEQUENCE GRAPH

. Write refers to either or both byte write enables (LW, UW).

BURST SEQUENCE GRAPH

(See Note)

1,0

1,1

0,0

0,1

A1

′

, A0

′

=

NOTE: The external two values for A1 and A0

provide the starting point for the burst

sequence graph. The burst logic ad-

vances A1 and A0 as shown above.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC2003SG66 | 256KB and 512KB BurstRAM Secondary Cache Module for PowerPC - Based Systems |

| MPC2104PDG66 | 256KB/512KB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2104P | 256KB/512KB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2105CDG66 | 512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2105C | 512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC2003SG66 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:256KB and 512KB BurstRAM Secondary Cache Module for PowerPC - Based Systems |

| MPC2004 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:256KB and 512KB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2005 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:256KB and 512KB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC202025T | 制造商:AMEC THERMASOL 功能描述:HEAT SINK CERAMIC 20*20*2.5TD ADHESIV 制造商:AMEC THERMASOL 功能描述:HEAT SINK, CERAMIC 20*20*2.5STD ADHESIV 制造商:AMEC THERMASOL 功能描述:HEAT SINK; Thermal Resistance:10.21C/W; External Height - Imperial:0.098"; External Height - Metric:2.5mm; External Width - Imperial:0.787"; External Width - Metric:20mm; External Length - Imperial:0.787"; Heat Sink Material:Ceramic;RoHS Compliant: Yes |

| MPC2104 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:256KB and 512KB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。