- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25629 > MPC8547CVUAQGA (FREESCALE SEMICONDUCTOR INC) 32-BIT, 1000 MHz, MICROPROCESSOR, CBGA783 PDF資料下載

參數(shù)資料

| 型號(hào): | MPC8547CVUAQGA |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 1000 MHz, MICROPROCESSOR, CBGA783 |

| 封裝: | 29 X 29 MM, 1 MM PITCH, FLIP CHIP, LEAD FREE, CERAMIC, BGA-783 |

| 文件頁(yè)數(shù): | 112/142頁(yè) |

| 文件大小: | 1504K |

| 代理商: | MPC8547CVUAQGA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)當(dāng)前第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

Freescale Semiconductor

71

PCI Express

16.4.2

Transmitter Compliance Eye Diagrams

The TX eye diagram in Figure 48 is specified using the passive compliance/test measurement load (see

Figure 50) in place of any real PCI Express interconnect +RX component.

There are two eye diagrams that must be met for the transmitter. Both eye diagrams must be aligned in

time using the jitter median to locate the center of the eye diagram. The different eye diagrams will differ

in voltage depending whether it is a transition bit or a de-emphasized bit. The exact reduced voltage level

of the de-emphasized bit will always be relative to the transition bit.

The eye diagram must be valid for any 250 consecutive UIs.

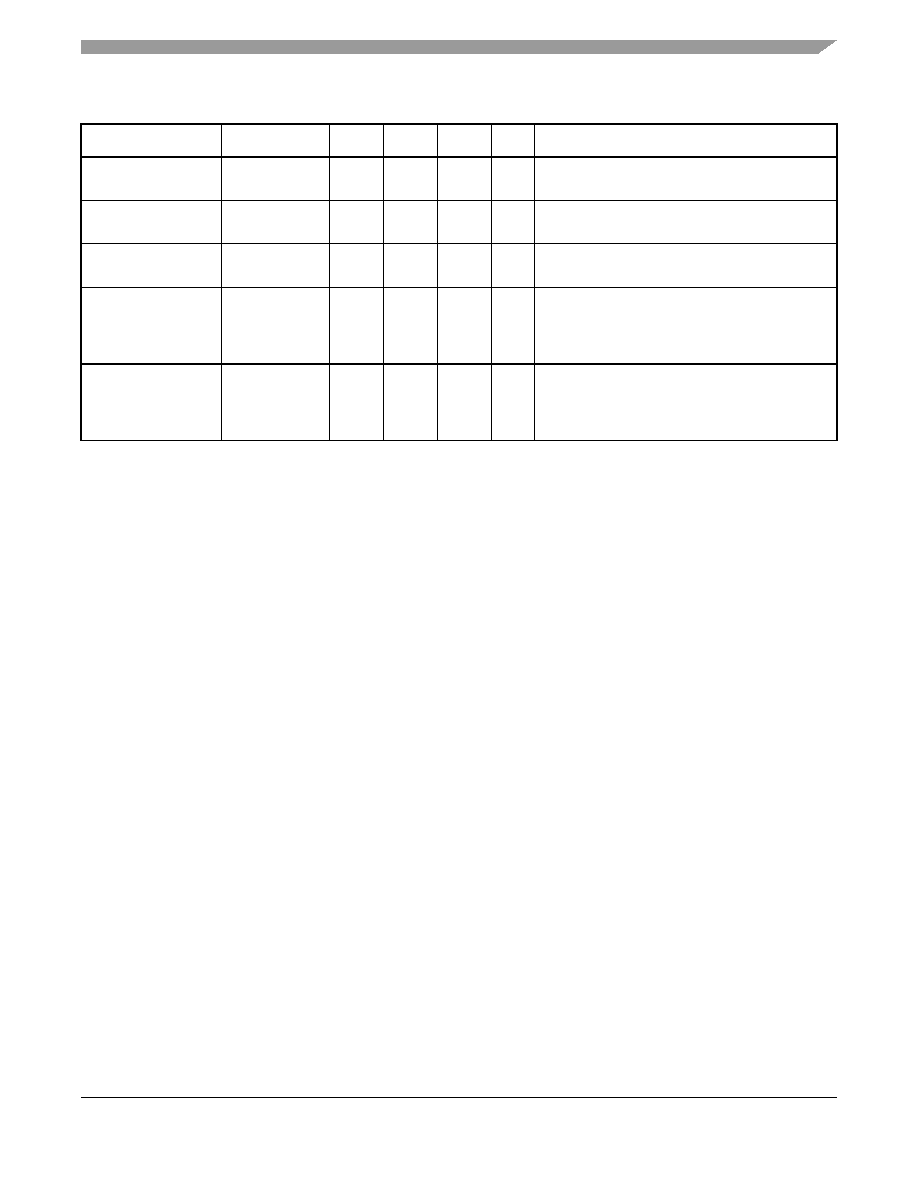

ZTX-DIFF-DC

DC differential

TX impedance

80

100

120

Ω

TX DC differential mode low impedance

ZTX-DC

Transmitter DC

impedance

40

—

Ω

Required TX D+ as well as D– DC impedance

during all states

LTX-SKEW

Lane-to-lane

output skew

—

500

+2 UI

ps

Static skew between any two transmitter lanes

within a single Link

CTX

AC coupling

capacitor

75

—

200

nF

All transmitters shall be AC coupled. The AC

coupling is required either within the media or

within the transmitting component itself. See note

8.

Tcrosslink

Crosslink

random timeout

0

—

1

ms

This random timeout helps resolve conflicts in

crosslink configuration by eventually resulting in

only one downstream and one upstream port.

See Note 7.

Notes:

1. No test load is necessarily associated with this value.

2. Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 50 and measured over

any 250 consecutive TX UIs. (Also refer to the transmitter compliance eye diagram shown in Figure 48.)

3. A TTX-EYE = 0.70 UI provides for a total sum of deterministic and random jitter budget of TTX-JITTER-MAX = 0.30 UI for the

transmitter collected over any 250 consecutive TX UIs. The TTX-EYE-MEDIAN-to-MAX-JITTER median is less than half of the total

TX jitter budget collected over any 250 consecutive TX UIs. It should be noted that the median is not the same as the mean.

The jitter median describes the point in time where the number of jitter points on either side is approximately equal as

opposed to the averaged time value.

4. The transmitter input impedance shall result in a differential return loss greater than or equal to 12 dB and a common mode

return loss greater than or equal to 6 dB over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement

applies to all valid input levels. The reference impedance for return loss measurements is 50

Ω to ground for both the D+ and

D– line (that is, as measured by a vector network analyzer with 50-

Ω probes—see Figure 50). Note that the series capacitors

CTX is optional for the return loss measurement.

5. Measured between 20%–80% at transmitter package pins into a test load as shown in Figure 50 for both VTX-D+ and VTX-D–.

6. See Section 4.3.1.8 of the

PCI Express Base Specifications Rev 1.0a.

7. See Section 4.2.6.3 of the

PCI Express Base Specifications Rev 1.0a.

8. MPC8548E SerDes transmitter does not have CTX built in. An external AC coupling capacitor is required.

Table 52. Differential Transmitter (TX) Output Specifications (continued)

Symbol

Parameter

Min

Nom

Max

Unit

Comments

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC8547ECVUAQJA | 32-BIT, 1000 MHz, MICROPROCESSOR, CBGA783 |

| MPC8547ECVUATGB | 32-BIT, 1200 MHz, MICROPROCESSOR, CBGA783 |

| MPC8547EVTAUGB | 32-BIT, 1000 MHz, MICROPROCESSOR, PBGA783 |

| MPC8547HXAQJ | 32-BIT, 1000 MHz, MICROPROCESSOR, CBGA783 |

| MPC8548CPXATGB | 32-BIT, 1200 MHz, MICROPROCESSOR, PBGA783 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8547ECHXAQG | 功能描述:微處理器 - MPU PQ38 8548E RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8547ECHXAUJ | 功能描述:微處理器 - MPU PQ38 8548E RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8547ECPXAQGA | 功能描述:微處理器 - MPU PQ3 8547E Storage Processor RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8547ECPXAQGB | 功能描述:微處理器 - MPU FG PQ38 8548 RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8547ECPXAQGD | 功能描述:微處理器 - MPU PQ38 PB XT WE 1000 R3.0 RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。