- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄45265 > MR80C32-36:RD (ATMEL CORP) 8-BIT, 36 MHz, MICROCONTROLLER, CQCC44 PDF資料下載

參數(shù)資料

| 型號(hào): | MR80C32-36:RD |

| 廠商: | ATMEL CORP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 36 MHz, MICROCONTROLLER, CQCC44 |

| 封裝: | LCC-44 |

| 文件頁(yè)數(shù): | 2/120頁(yè) |

| 文件大小: | 25028K |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)

10

8272E–AVR–04/2013

ATmega164A/PA/324A/PA/644A/PA/1284/P

7.

AVR CPU Core

7.1

Overview

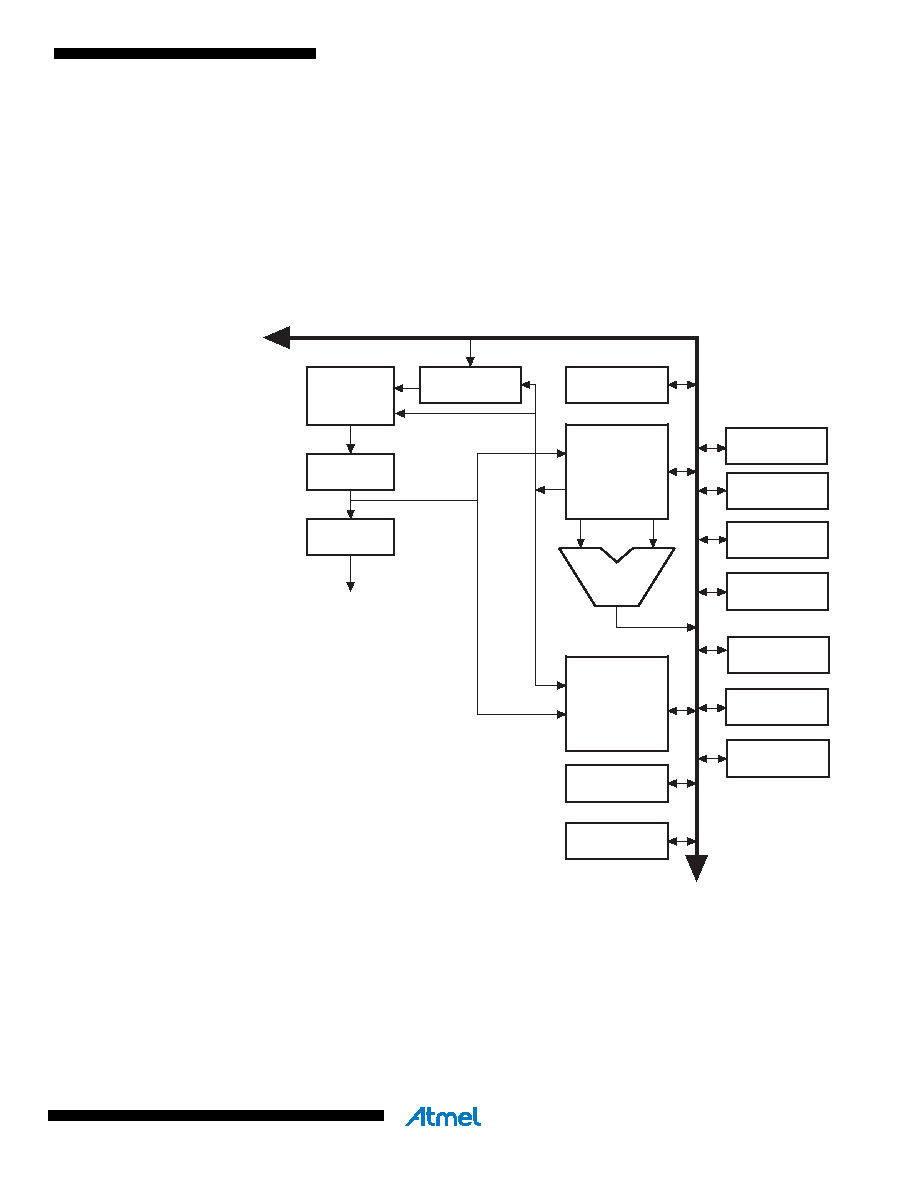

This section discusses the AVR core architecture in general. The main function of the CPU core

is to ensure correct program execution. The CPU must therefore be able to access memories,

perform calculations, control peripherals, and handle interrupts.

Figure 7-1.

Block diagram of the AVR architecture.

In order to maximize performance and parallelism, the AVR uses a Harvard architecture – with

separate memories and buses for program and data. Instructions in the program memory are

executed with a single level pipelining. While one instruction is being executed, the next instruc-

tion is pre-fetched from the program memory. This concept enables instructions to be executed

in every clock cycle. The program memory is In-System Reprogrammable Flash memory.

The fast-access Register File contains 32 x 8-bit general purpose working registers with a single

clock cycle access time. This allows single-cycle Arithmetic Logic Unit (ALU) operation. In a typ-

Flash

Program

Memory

Instruction

Register

Instruction

Decoder

Program

Counter

Control Lines

32 x 8

General

Purpose

Registrers

ALU

Status

and Control

I/O Lines

EEPROM

Data Bus 8-bit

Data

SRAM

Direct

Addressing

Indirect

Addressing

Interrupt

Unit

SPI

Unit

Watchdog

Timer

Analog

Comparator

I/O Module 2

I/O Module1

I/O Module n

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MQ80C32E-30/883:RD | 8-BIT, 30 MHz, MICROCONTROLLER, CQFP44 |

| MC80C32E-36/883 | 8-BIT, 36 MHz, MICROCONTROLLER, CDIP40 |

| MC80C52TXXX-36/883:D | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CDIP40 |

| MD80C52TXXX-30SHXXX:D | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, CDIP40 |

| MR80C32E-36SHXXX:D | 8-BIT, 36 MHz, MICROCONTROLLER, CQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MR80C51BH | 制造商:ROCHESTER 制造商全稱:ROCHESTER 功能描述:CMOS SINGLE - CHIP 8-BIT MICROCOMPUTER 64K program Memory Space |

| MR80C86 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86/B | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述:Microprocessor, 16 Bit, 44 Pin, Ceramic, LCC |

| MR80C86-2 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86-2/883 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。