- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25632 > MR80C32E-25SBD (ATMEL CORP) 8-BIT, 25 MHz, MICROCONTROLLER, CQCC44 PDF資料下載

參數(shù)資料

| 型號: | MR80C32E-25SBD |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 25 MHz, MICROCONTROLLER, CQCC44 |

| 封裝: | LCC-44 |

| 文件頁數(shù): | 216/310頁 |

| 文件大?。?/td> | 4427K |

| 代理商: | MR80C32E-25SBD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁當(dāng)前第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁第238頁第239頁第240頁第241頁第242頁第243頁第244頁第245頁第246頁第247頁第248頁第249頁第250頁第251頁第252頁第253頁第254頁第255頁第256頁第257頁第258頁第259頁第260頁第261頁第262頁第263頁第264頁第265頁第266頁第267頁第268頁第269頁第270頁第271頁第272頁第273頁第274頁第275頁第276頁第277頁第278頁第279頁第280頁第281頁第282頁第283頁第284頁第285頁第286頁第287頁第288頁第289頁第290頁第291頁第292頁第293頁第294頁第295頁第296頁第297頁第298頁第299頁第300頁第301頁第302頁第303頁第304頁第305頁第306頁第307頁第308頁第309頁第310頁

293

7799D–AVR–11/10

ATmega8U2/16U2/32U2

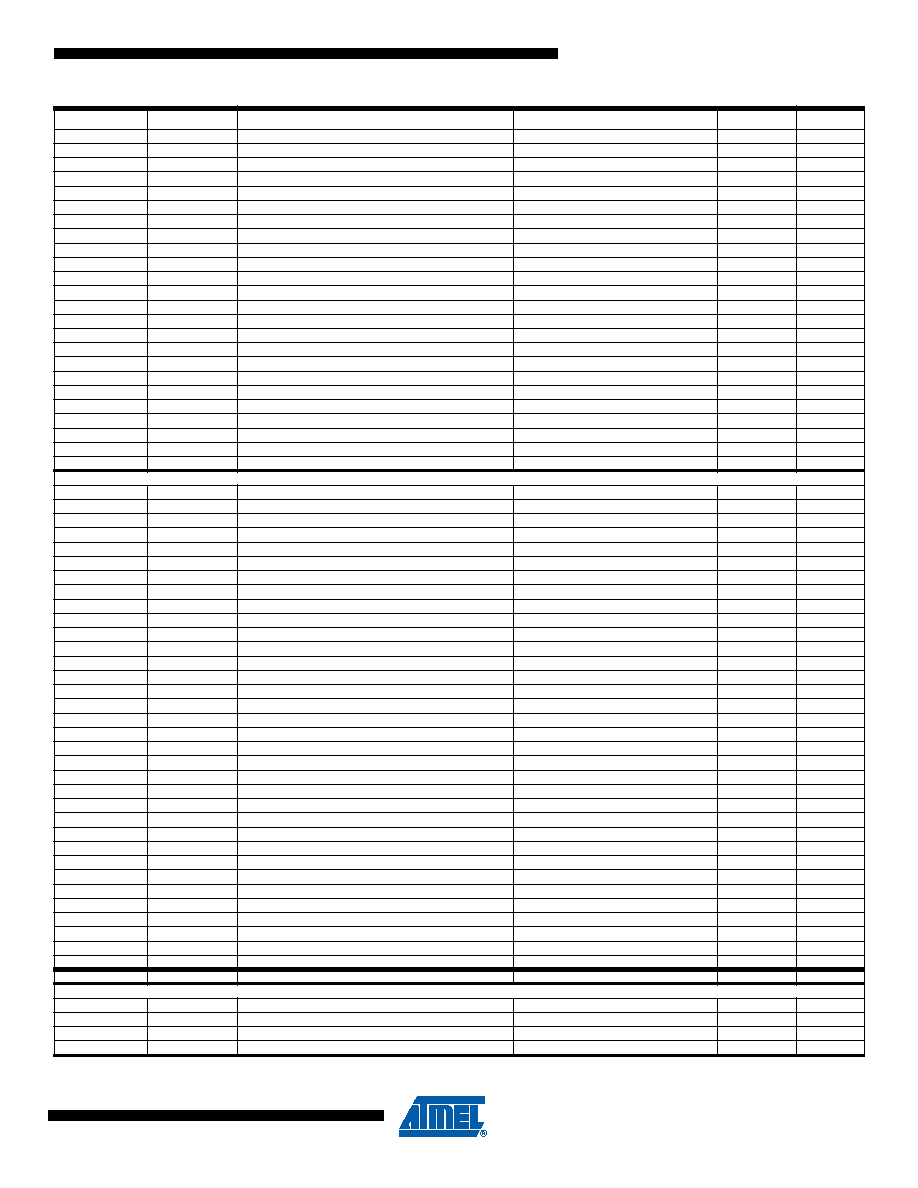

ROL

Rd

Rotate Left Through Carry

Rd(0)

C,Rd(n+1) Rd(n),CRd(7)

Z,C,N,V

1

ROR

Rd

Rotate Right Through Carry

Rd(7)

C,Rd(n) Rd(n+1),CRd(0)

Z,C,N,V

1

ASR

Rd

Arithmetic Shift Right

Rd(n)

Rd(n+1), n=0..6

Z,C,N,V

1

SWAP

Rd

Swap Nibbles

Rd(3..0)

Rd(7..4),Rd(7..4)Rd(3..0)

None

1

BSET

s

Flag Set

SREG(s)

1

SREG(s)

1

BCLR

s

Flag Clear

SREG(s)

0

SREG(s)

1

BST

Rr, b

Bit Store from Register to T

T

Rr(b)

T

1

BLD

Rd, b

Bit load from T to Register

Rd(b)

T

None

1

SEC

Set Carry

C

1C

1

CLC

Clear Carry

C

0

C

1

SEN

Set Negative Flag

N

1N

1

CLN

Clear Negative Flag

N

0

N

1

SEZ

Set Zero Flag

Z

1Z

1

CLZ

Clear Zero Flag

Z

0

Z

1

SEI

Global Interrupt Enable

I

1I

1

CLI

Global Interrupt Disable

I

0

I

1

SES

Set Signed Test Flag

S

1S

1

CLS

Clear Signed Test Flag

S

0

S

1

SEV

Set Twos Complement Overflow.

V

1V

1

CLV

Clear Twos Complement Overflow

V

0

V

1

SET

Set T in SREG

T

1T

1

CLT

Clear T in SREG

T

0

T

1

SEH

Set Half Carry Flag in SREG

H

1H

1

CLH

Clear Half Carry Flag in SREG

H

0

H

1

DATA TRANSFER INSTRUCTIONS

MOV

Rd, Rr

Move Between Registers

Rd

Rr

None

1

MOVW

Rd, Rr

Copy Register Word

Rd+1:Rd

Rr+1:Rr

None

1

LDI

Rd, K

Load Immediate

Rd

K

None

1

LD

Rd, X

Load Indirect

Rd

(X)

None

2

LD

Rd, X+

Load Indirect and Post-Inc.

Rd

(X), X X + 1

None

2

LD

Rd, - X

Load Indirect and Pre-Dec.

X

X - 1, Rd (X)

None

2

LD

Rd, Y

Load Indirect

Rd

(Y)

None

2

LD

Rd, Y+

Load Indirect and Post-Inc.

Rd

(Y), Y Y + 1

None

2

LD

Rd, - Y

Load Indirect and Pre-Dec.

Y

Y - 1, Rd (Y)

None

2

LDD

Rd,Y+q

Load Indirect with Displacement

Rd

(Y + q)

None

2

LD

Rd, Z

Load Indirect

Rd

(Z)

None

2

LD

Rd, Z+

Load Indirect and Post-Inc.

Rd

(Z), Z Z+1

None

2

LD

Rd, -Z

Load Indirect and Pre-Dec.

Z

Z - 1, Rd (Z)

None

2

LDD

Rd, Z+q

Load Indirect with Displacement

Rd

(Z + q)

None

2

LDS

Rd, k

Load Direct from SRAM

Rd

(k)

None

2

ST

X, Rr

Store Indirect

(X)

Rr

None

2

ST

X+, Rr

Store Indirect and Post-Inc.

(X)

Rr, X X + 1

None

2

ST

- X, Rr

Store Indirect and Pre-Dec.

X

X - 1, (X) Rr

None

2

ST

Y, Rr

Store Indirect

(Y)

Rr

None

2

ST

Y+, Rr

Store Indirect and Post-Inc.

(Y)

Rr, Y Y + 1

None

2

ST

- Y, Rr

Store Indirect and Pre-Dec.

Y

Y - 1, (Y) Rr

None

2

STD

Y+q,Rr

Store Indirect with Displacement

(Y + q)

Rr

None

2

ST

Z, Rr

Store Indirect

(Z)

Rr

None

2

ST

Z+, Rr

Store Indirect and Post-Inc.

(Z)

Rr, Z Z + 1

None

2

ST

-Z, Rr

Store Indirect and Pre-Dec.

Z

Z - 1, (Z) Rr

None

2

STD

Z+q,Rr

Store Indirect with Displacement

(Z + q)

Rr

None

2

STS

k, Rr

Store Direct to SRAM

(k)

Rr

None

2

LPM

Load Program Memory

R0

(Z)

None

3

LPM

Rd, Z

Load Program Memory

Rd

(Z)

None

3

LPM

Rd, Z+

Load Program Memory and Post-Inc

Rd

(Z), Z Z+1

None

3

SPM

Store Program Memory

(Z)

R1:R0

None

-

IN

Rd, P

In Port

Rd

P

None

1

OUT

P, Rr

Out Port

P

Rr

None

1

PUSH

Rr

Push Register on Stack

STACK

Rr

None

2

POP

Rd

Pop Register from Stack

Rd

STACK

None

2

MCU CONTROL INSTRUCTIONS

NOP

No Operation

None

1

SLEEP

Sleep

(see specific descr. for Sleep function)

None

1

WDR

Watchdog Reset

(see specific descr. for WDR/timer)

None

1

BREAK

Break

For On-chip Debug Only

None

N/A

Mnemonics

Operands

Description

Operation

Flags

#Clocks

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MR80C154-12P883R | 8-BIT, 12 MHz, MICROCONTROLLER, CQCC44 |

| MQ83C154TXXX-12P883R | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQFP44 |

| MD83C154DTXXX-12/883D | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CDIP40 |

| MQ83C154CXXX-20/883D | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQFP44 |

| MQ80C52XXX-12SCD | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MR80C51BH | 制造商:ROCHESTER 制造商全稱:ROCHESTER 功能描述:CMOS SINGLE - CHIP 8-BIT MICROCOMPUTER 64K program Memory Space |

| MR80C86 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86/B | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述:Microprocessor, 16 Bit, 44 Pin, Ceramic, LCC |

| MR80C86-2 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86-2/883 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。