- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25633 > MR80C52EXXX-25/883 (ATMEL CORP) 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQCC44 PDF資料下載

參數(shù)資料

| 型號: | MR80C52EXXX-25/883 |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQCC44 |

| 封裝: | LCC-44 |

| 文件頁數(shù): | 9/46頁 |

| 文件大小: | 4720K |

| 代理商: | MR80C52EXXX-25/883 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

16

ATtiny20 [DATASHEET]

8235E–AVR–03/2013

The non-volatile memory lock bits and all the Flash memory sections are mapped to the data memory space. These

locations appear as read-only for device firmware.

The four different addressing modes for data memory are direct, indirect, indirect with pre-decrement, and indirect with

post-increment. In the register file, registers R26 to R31 function as pointer registers for indirect addressing.

The IN and OUT instructions can access all 64 locations of I/O memory. Direct addressing using the LDS and STS

instructions reaches the 128 locations between 0x0040 and 0x00BF.

The indirect addressing reaches the entire data memory space. When using indirect addressing modes with automatic

pre-decrement and post-increment, the address registers X, Y, and Z are decremented or incremented.

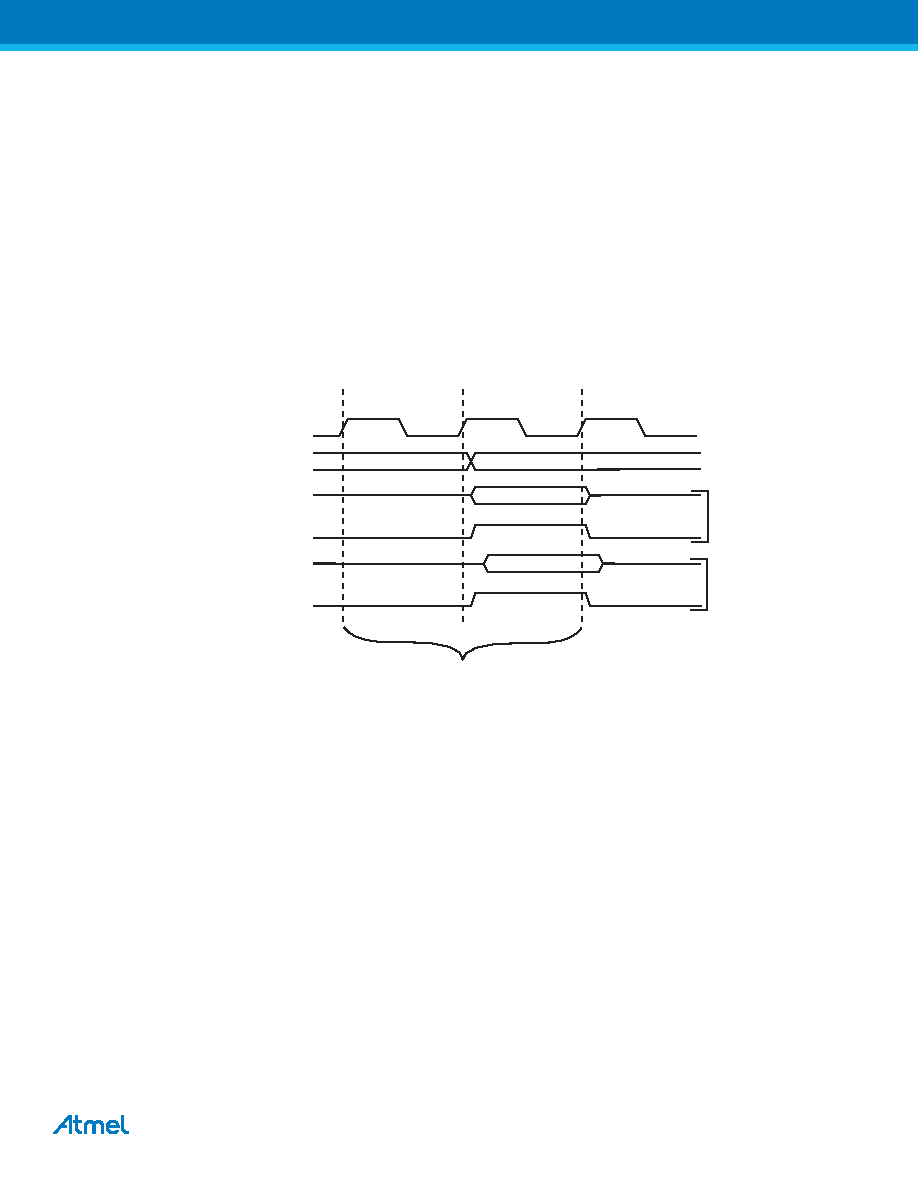

5.2.1

Data Memory Access Times

This section describes the general access timing concepts for internal memory access. The internal data SRAM access

Figure 5-2.

On-chip Data SRAM Access Cycles

5.3

I/O Memory

The I/O space definition of the ATtiny20 is shown in “Register Summary” on page 203.

All ATtiny20 I/Os and peripherals are placed in the I/O space. All I/O locations may be accessed using the LD and ST

instructions, enabling data transfer between the 16 general purpose working registers and the I/O space. I/O Registers

within the address range 0x00 - 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the

value of single bits can be checked by using the SBIS and SBIC instructions. See document “AVR Instruction Set” and

section “Instruction Set Summary” on page 205 for more details. When using the I/O specific commands IN and OUT, the

I/O addresses 0x00 - 0x3F must be used.

For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory

addresses should never be written.

Some of the status flags are cleared by writing a logical one to them. Note that CBI and SBI instructions will only operate

on the specified bit, and can therefore be used on registers containing such status flags. The CBI and SBI instructions

work on registers in the address range 0x00 to 0x1F, only.

The I/O and Peripherals Control Registers are explained in later sections.

clk

WR

RD

Data

Address

Address valid

T1

T2

T3

Compute Address

Read

Wr

ite

CPU

Memory Access Instruction

Next Instruction

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MQ83C154XXX-12/883R | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQFP44 |

| MC80C52CXXX-16P883 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 |

| MC80C32-12SBD | 8-BIT, 12 MHz, MICROCONTROLLER, CDIP40 |

| MR83C154DCXXX-25P883 | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQCC44 |

| MC80C52EXXX-30SHXXX:D | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MR80C86 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86/B | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述:Microprocessor, 16 Bit, 44 Pin, Ceramic, LCC |

| MR80C86-2 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86-2/883 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MR80C86-2/B | 制造商:Intersil Corporation 功能描述:MPU 80C86 16BIT CMOS 8MHZ 44PLCC - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。