- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371146 > MRFIC1859 (Motorola, Inc.) Dual-Band GSM 3.6V Integrated RF Power Amplifier(GSM 3.6V集成式射頻功放) PDF資料下載

參數(shù)資料

| 型號: | MRFIC1859 |

| 廠商: | Motorola, Inc. |

| 英文描述: | Dual-Band GSM 3.6V Integrated RF Power Amplifier(GSM 3.6V集成式射頻功放) |

| 中文描述: | 雙頻GSM 3.6V的集成RF功率放大器(手機3.6V的集成式射頻功放) |

| 文件頁數(shù): | 11/15頁 |

| 文件大小: | 180K |

| 代理商: | MRFIC1859 |

MRFIC1859

11

MOTOROLA WIRELESS SEMICONDUCTOR

SOLUTIONS – RF AND IF DEVICE DATA

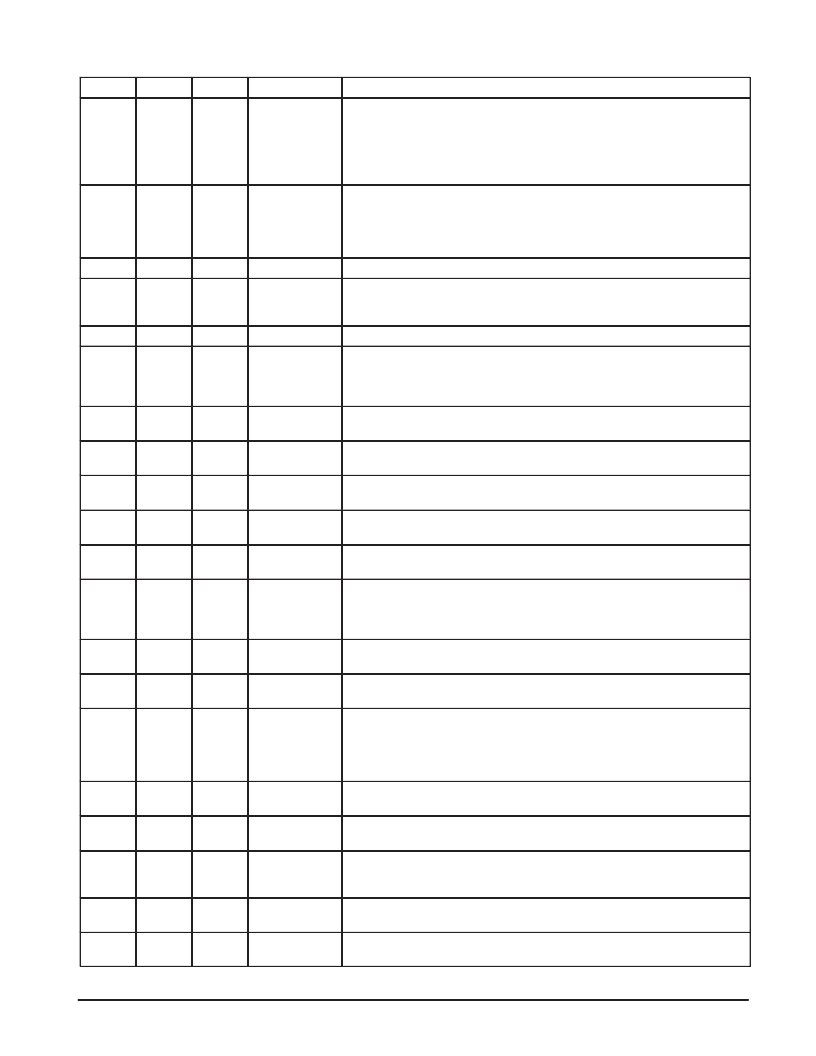

PIN FUNCTION DESCRIPTION

Pin No.

Symbol

I/O

Description

Functionality

1

B23G

I

GSM Bias for

2nd and 3rd

stage

Bias pin of GSM second and third stages. Biasing circuit is made of an internal

resistor connected to RF transistor gate, and in series with a current source,

connected to VSS (Pin 32). An external resistor allows to tune biasing point for best

gain (Class AB). To switch off GSM line–up, setting this pin (and Pin 18) to high

impedance, which will apply VSS (–5.0 V) to the gates, i.e., a voltage two times

lower than FET threshold voltage.

2

VP

O

Positive voltage

A buffer amplifier is designed to produce the required negative voltage, based on

RF signal amplification and rectification. Also a positive voltage is generated in the

same way, with rectification and a voltage doubler. This voltage supplies an op amp

in order to drive a NMOS as drain switch. Refer to application schematic, with

MC33170 and MTSF3N02 (products of On Semiconductor).

3

Gnd

Ground

4,5,6,7,8

OutG

O

GSM output

RF output and power supply for output GSM stage. Supply voltage is provided

through those five pins. An external matching network is required to provide

optimum load impedance.

9

N.C.

10,11,12

D2G

I

GSM 2nd stage

drain

Power supply for GSM second stage, and inter–stage matching. Wire bonds and

pins form the required inductor for optimum inter–matching tuning. Make note that

decoupling capacitor on those pins needs to be placed as close as possible to the

pins. Refer to application schematic for component value.

13

D1D

I

DCS 1st stage

drain

Power supply for DCS first stage, and inter–staging matching. This pin associated

with a printed line (80

) forms the required inductor for a proper match.

14

D1B

I

Buffer 1st stage

drain

Power supply for buffer amplifier first stage, and inter–staging matching. This pin,

associated with a printed line (80

) forms the required inductor for a proper match.

15

B1D

I

DCS 1st stage

Bias

Same function as Pin 18 for DCS amplifier.

16

InD

I

DCS RF Input

RF input for DCS amplifier. A series inductor or line and a parallel inductor are

required for a proper matching to 50

and maximum gain. See application circuit.

17

InG

I

GSM RF Input

RF input for GSM amplifier. An inductor and a capacitor are required for a proper

matching to 50

and maximum gain. See application circuit.

18

B1G

I

GSM 1st stage

Bias

Bias pin of GSM first stage and associated buffer stage. Biasing circuit is made of

an internal resistor connected to RF transistor gate, and in series with a current

source, connected to VSS (Pin 32). An external resistor allows to tune biasing point

for best gain (Class AB). See comments on Pin 1.

19

D1G

I

GSM 1st stage

drain

Power supply for GSM first stage, and inter–stage matching. This pin, associated

with a printed line (80

) form the required inductor for a proper match.

20

G2D

I

DCS 2nd stage

gate

Access to DCS 2nd stage gate. A shunt capacitor connected to this pin contributes

to the inter–stage matching between 1st and 2nd DCS stages.

21

VSC

O

Check for

Negative voltage

An opened drain transistor connected to this pin, with VSS as gate voltage, gives a

checking signal for negative voltage generation. Used in application circuit to forbid

on state to the NMOS Drain switch when VSS is not working. Prevents IC

degradation when bias is not present. This pin is not used with MC33170 which has

its own protection circuit.

22,23

D2D

I

DCS 2nd stage

drain

Power supply for DCS driver stage, and inter–staging matching. These pins form

the required inductor for a proper match.

24

B23D

I

DCS Bias for 2nd

and 3rd stage

Same as Pin 1 for DCS amplifier.

25,26,27,

28,29

OutD

O

DCS RF Output

RF output and power supply for output DCS stage. Supply voltage is provided

through those five pins. An external matching network is required to provide

optimum load impedance.

30

B2B

I

Buffer 2nd state

Bias

Like Pins 1, 15, and 18, this is a bias pin. Pin 30 is used to bias 2nd stage of buffer

amplifier.

31

D2B

I

Buffer 2nd stage

Drain

Drain supply and matching of buffer amplifier to maximize VSS and VP voltages.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MRW54001 | MICROWAVE LINEAR POWER TRANSISTORS |

| MSB709-RT1 | PNP General Purpose Amplifier Transistor Surface Mount |

| MSB709-RT1 | PNP General Purpose Amplifier Transistor Surface Mount |

| MSB709RT1 | PNP General Purpose Amplifier Transistor Surface Mount |

| MSB709-RT1 | PNP General Purpose Amplifier Transistor Surface Mount |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MRFIC1870 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:3.2 V DCS/PCS GaAs Integrated Power Amplifier |

| MRFIC1870D | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:3.2 V DCS/PCS GaAs Integrated Power Amplifier |

| MRFIC1870PP | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:3.2 V DCS/PCS GaAs Integrated Power Amplifier |

| MRFIC1884 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Dual-Band CDMA Upconverter |

| MRFIC1884R2 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Dual-Band CDMA Upconverter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。