- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄45389 > MSM62X42BGS-1K (LAPIS SEMICONDUCTOR CO LTD) 1 TIMER(S), REAL TIME CLOCK, PDSO24 PDF資料下載

參數(shù)資料

| 型號(hào): | MSM62X42BGS-1K |

| 廠商: | LAPIS SEMICONDUCTOR CO LTD |

| 元件分類(lèi): | 時(shí)鐘/數(shù)據(jù)恢復(fù)及定時(shí)提取 |

| 英文描述: | 1 TIMER(S), REAL TIME CLOCK, PDSO24 |

| 封裝: | PLASTIC, SOP-24 |

| 文件頁(yè)數(shù): | 6/28頁(yè) |

| 文件大小: | 219K |

| 代理商: | MSM62X42BGS-1K |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

Semiconductor

MSM62X42B

53

f) Regarding W

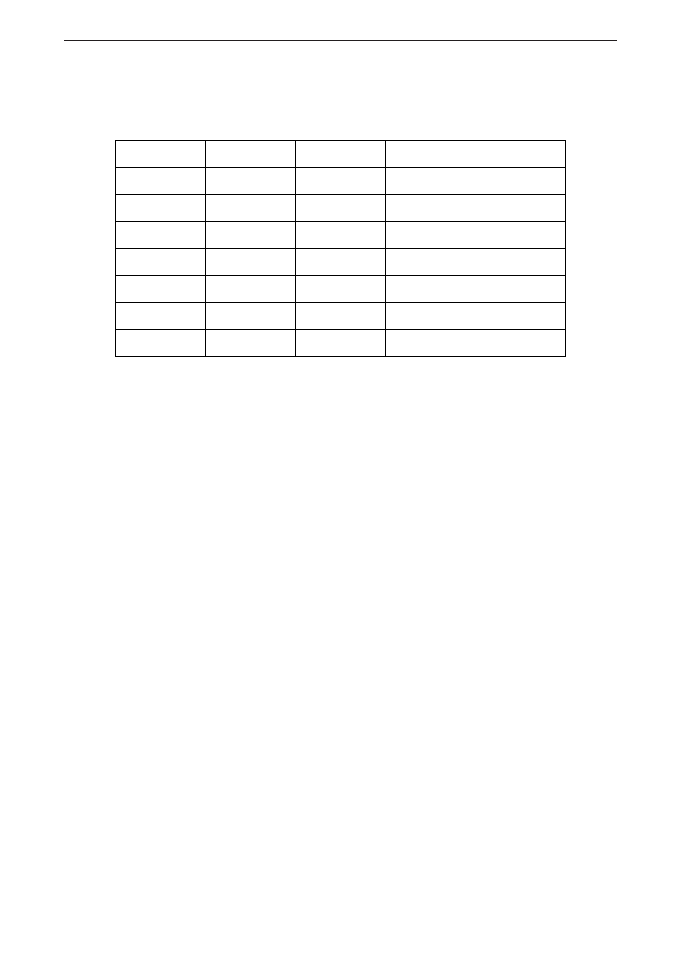

The Register W data limits are up-counted from 0 to 6. The following Table 1 shows a possible

data definition.

CD REGISTER (Control D Register)

a) HOLD (D0)

This Register is one means used for reading out registers S1 to W (addresses 0 to C) and

a bit used for writing. "1" bit to this bit is written and when BUSY bit shows "0", the clock

more than 1 second digit stops and the reading and writing become possible (Refer to the

item APPLICATION NOTE for reading which does not use HOLD bit). When BUSY was

"1" and after reading have finished, "0" is written to HOLD bit. If the writing of "0" is

omitted, then this results in the cause for erroneous data. Setting this bit to "1" inhibits

a carry to 1 second counter in the IC internal, but a carry to a second counter caused during

the duration of "1" is automatically compensated (+1 second) by only one time at the time

when "0" is written to this bit. However, the carry after the second is disregarded and is

not compensated (loss second).

If CS1 makes "L", the HOLD bit becomes equivalent to the writing to "0" and becomes "0".

b) BUSY (D1)

The status bit in the IC internal which shows the interface condition with a microcom-

puter. When the registers S1 to W (addresses 0 to C) is written, when HOLD bit is always

"1" and when BUSY bit is surely "0", in case the HOLD bit is used for reading, this is

performed when the BUSY bit is "0". "0" of the BUSY bit continues while the HOLD bit

is "1". When the HOLD bit makes "0", the BUSY bit becomes "1".

The operation for the registers CD, CE and CF is irrespectively performed for the HOLD

bit and BUSY bit.

The BUSY bit is "1" uncondiotinally when the HOLD bit=0 and when "1" written into the

HOLD bit, BUSY or not BUSY can be confirmed and when BUSY="1", "0" is once written

into the HOLD bit, and then "1" is again written. BUSY is checked. The routine procedure

like this [HOLD ¨ "0", HOLD ¨ "1", BUSY check] is repeated, or after "0" is written into

the HOLD bit, "1" is again written into the HOLD bit after 190

s and BUSY=0 is

confirmed.

The time when this IC is BUSY is 190

s per one second

The writing into the BUSY bit cannot be performed.

TABLE 1

W4

0

1

W2

0

1

0

1

W1

0

1

0

1

0

1

0

Day of Week

Sunday

Monday

Tuesday

Wednesday

Thursday

Friday

Saturday

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSM62X42BRS | 1 TIMER(S), REAL TIME CLOCK, PDIP18 |

| MSM62X42BGS-1K | REAL TIME CLOCK, PDSO24 |

| MSM62X42BRS | REAL TIME CLOCK, PDIP18 |

| MSM63182-XXXGS-K | 4-BIT, MROM, 2 MHz, MICROCONTROLLER, PQFP128 |

| MSM63182-XXX | 4-BIT, MROM, 2 MHz, MICROCONTROLLER, UUC107 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSM62X42BGS-1K-B | 制造商:OK International 功能描述: |

| MSM62X42BRS-A | 制造商:ROHM Semiconductor 功能描述: |

| MSM62X42BRS-B | 制造商:ROHM Semiconductor 功能描述: |

| MSM6307 | 制造商:OKI 制造商全稱(chēng):OKI electronic componets 功能描述:D2B TRANSCEIVER LSI |

| MSM6307GS-VK | 制造商:OKI 制造商全稱(chēng):OKI electronic componets 功能描述:D2B TRANSCEIVER LSI |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。