- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45389 > MSM6542-01MS-K (OKI ELECTRIC INDUSTRY CO LTD) 0 TIMER(S), REAL TIME CLOCK, PDSO20 PDF資料下載

參數(shù)資料

| 型號(hào): | MSM6542-01MS-K |

| 廠商: | OKI ELECTRIC INDUSTRY CO LTD |

| 元件分類: | 時(shí)鐘/數(shù)據(jù)恢復(fù)及定時(shí)提取 |

| 英文描述: | 0 TIMER(S), REAL TIME CLOCK, PDSO20 |

| 封裝: | 0.250 INCH, PLASTIC, SSOP-20 |

| 文件頁(yè)數(shù): | 15/54頁(yè) |

| 文件大小: | 406K |

| 代理商: | MSM6542-01MS-K |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)

Semiconductor

MSM6542-01/02/03

89

b)

IRQ FLAG

2 (D1) (Interrupt ReQuest FLAG2)

The status of this bit depends on the hardware output, low or open, from the ALARM OUT

pin for the MSM6542-03 or INTERRUPT OUT pin which uses a match with a set alarm time

as a trigger for the MSM6542-01/02. When hardware output is low, the bit is set at 1. When

it is open, the bit is set at 1.

The IRQ FLAG

2 bit is mainly used to indicate that there is an alarm timer interrupt for the

microcomputer. When the time set by alarm registers, A-S

1 to A-W, and the A-ENABLE

register expires with the D

1 (MASK2) bit of the CD register set at 0, hardware output changes

from open to low. At the same time, the IRQ FLAG

2 bit changes from 0 to 1.

When the D

3 (IT/PLS2) bit of the CD register is 1 (alarm interrupt mode), the IRQ FLAG2 bit

remains at 1 (hardware output is low) until the bit is read. When the bit is read, it is cleared.

However, when the IRQ FLAG

2 bit is read within about 122 s of occurrence of an alarm

interrupt with the D

0 (DP) bit of the CE' register set at 1, the IRQ FLAG2 bit is not cleared

immediately. It is cleared about 122

s after the interrupt occurs. When the bit is read at

least about 122

s after an interrupt occurs, it is cleared immediately.

In the alarm interrupt mode, writing 0 in the IRQ FLAG

2 bit does not clear the bit. When

another interrupt occurs with the bit set at 1, it is ignored.

When the D

3 (IT/PLS2) bit of the CD register is 0 (alarm pulse output mode), the IRQ FLAG2

bit remains at 1 (hardware output is low) until 0 is written in the bit or automatic restoration

is performed about 61

s later. When the IRQ FLAG

2 bit is read in the alarm pulse output

mode, it is not cleared.

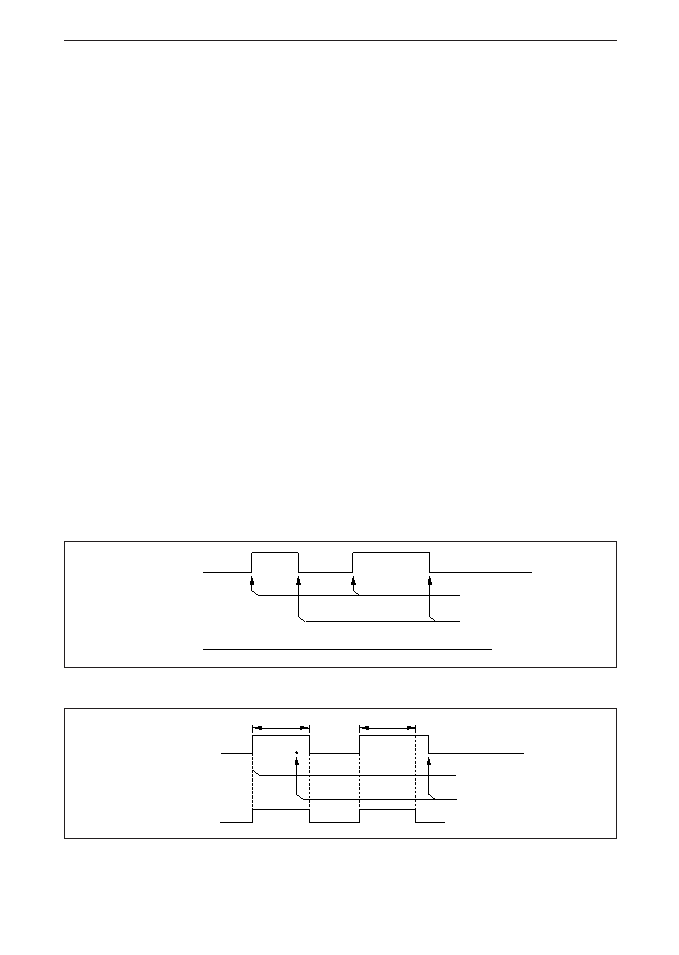

i)

In the alarm interrupt mode (when the IT/PLS

2 bit is 1)

(i-1)

When DP is 0:

(i-2)

When DP is 1:

The IRQ FLAG2 bit is read

Alarm interrupt timing

"0"

"1"

"0"

IRQ FLAG2

IRQ FLAG0

The IRQ FLAG2 bit is read

Alarm interrupt timing

"0"

"1"

"0"

IRQ FLAG2

IRQ FLAG0

122s

"1"

Note:

When the IRQ FLAG

2 bit is read within the 122 s interval with the

MASK

1 bit set at 1, it is not cleared. The IRQ FLAG2 bit is cleared after

the 122

s interval ends.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSM6542-02RS | 0 TIMER(S), REAL TIME CLOCK, PDIP18 |

| MSM6542-03GS-VK | 0 TIMER(S), REAL TIME CLOCK, PDSO24 |

| MSM6542-03RS | 0 TIMER(S), REAL TIME CLOCK, PDIP24 |

| MSM65513-GS-VK | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP64 |

| MSM65513-JS | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQCC68 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSM6542-02 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:REAL TIME CLOCK WITH PERIODIC AND ALARM OUTPUT |

| MSM6542-02RS | 制造商:ROHM Semiconductor 功能描述: |

| MSM6542-03 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:REAL TIME CLOCK WITH PERIODIC AND ALARM OUTPUT |

| MSM6544 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:42-DOT LCD DRIVER |

| MSM6544GS-2KR1 | 制造商:ROHM Semiconductor 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。