- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45392 > MSM80C85AHGS-2K (OKI ELECTRIC INDUSTRY CO LTD) 8-BIT, 5 MHz, MICROPROCESSOR, PQFP44 PDF資料下載

參數(shù)資料

| 型號(hào): | MSM80C85AHGS-2K |

| 廠商: | OKI ELECTRIC INDUSTRY CO LTD |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 5 MHz, MICROPROCESSOR, PQFP44 |

| 封裝: | PLASTIC, QFP-44 |

| 文件頁數(shù): | 29/31頁 |

| 文件大?。?/td> | 427K |

| 代理商: | MSM80C85AHGS-2K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁

7

Semiconductor

MSM80C85AHRS/GS/JS

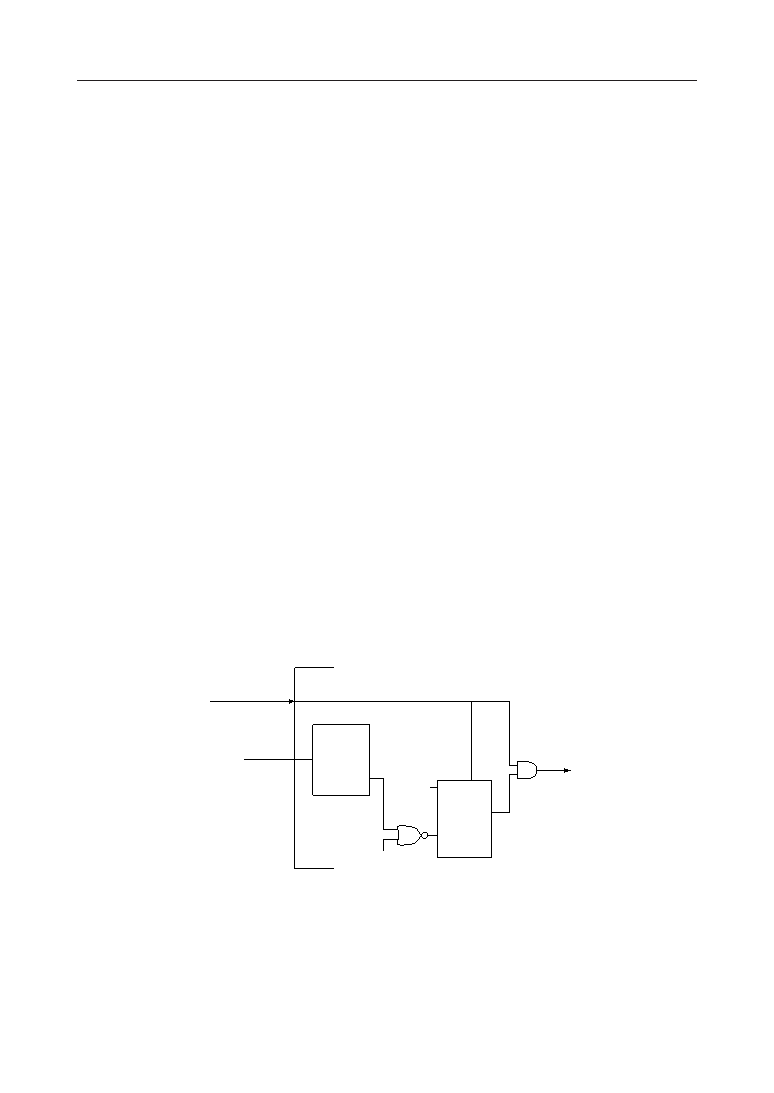

For RST 7.5, only a pulse is required to set an internal flip-flop which generates the internal

interrupt request. The RST 7.5 request flip-flop remains set until the request is serviced. Then

it is reset automatically, This flip-flop may also be reset by using the SIM instruction or by

issuing a RESET IN to the MSM80C85AH. The RST 7.5 internal flip-flop will be set by a pulse

on the RST 7.5 pin even when the RST 7.5 interrupt is masked out.

The interrupts are arranged in a flixed priority that determines which interrupt is to be

recognized if more than one is pending, as follows: TRAP-highest priority, RST 7.5, RST 6.5, RST

5.5, INTR-lowest priority. This priority scheme does not take into account the priority of a

routine that was started by a higher priority interrupt. RST 5.5 can interrupt an RST 7.5 routine

if the interrupt are re-enabled before the end of the RST 7.5 routine.

The TRAP interrupt is useful for catastrophic evens such as power failure or bus error. The

TRAP input is recognized just as any other interrupt but has the highest priority. It is not

affected by any flag or mask. The TRAP input is both edge and level sensitive. The TRAP input

must go high and remain high until it is acknowledged. It will not be recognized again until it

goes low, then high again. This avoids any false triggering due to noise or logic glitches. Figure

3 illustrates the TRAP interrupt request circuitry within the MSM80C85AH. Note that the

servicing of any interrupt (TRAP, RST 7.5, RST 6.5, RST 5.5,INTR) disables all future interrupts

(except TRAPs) until an El instruction is executed.

The TRAP interrupt is special in that it disables interrupts, but preserves the previous interrupt

enable status. Performing the first RIM instruction following a TRAP interrupt allows you to

determine whether interrupts were enabled or disabled prior to the TRAP. All subsequent RIM

instructions provide current interrupt enable status. Performing a RIM instruction following

INTR or RST 5.5-7.5 will provide current interrupt Enable status, revealing that Interrupts are

disabled.

The serial I/O system is also controlled by the RIM and SIM instructions. SID is read by RIM,

and SIM sets the SOD data.

Inside the MSM80C85AH

External TRAP

Interrupt Request

TRAP

Schmitt

Trigger

RESET IN

RESET

TRAP

Interrupt

Request

+5 V

D

CLK

D

Q

F/F

Clear

TRAP F.F

Internal

TRAP

Acknowledge

Figure 3 Trap and

RESET IN Circuit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSM80C85AHRS | 8-BIT, 5 MHz, MICROPROCESSOR, PDIP40 |

| MSM80C86A-10RS | 16-BIT, 10 MHz, MICROPROCESSOR, PDIP40 |

| MSM80C88A-10GS | 8-BIT, 10 MHz, MICROPROCESSOR, PQFP56 |

| MSM80C88A-10RS | 8-BIT, 10 MHz, MICROPROCESSOR, PDIP40 |

| MSM80C88A-10JS | 8-BIT, 10 MHz, MICROPROCESSOR, PQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSM80C85AHJS | 制造商:ROHM Semiconductor 功能描述: |

| MSM80C85AHRS | 制造商:OK International 功能描述: 制造商:ROHM Semiconductor 功能描述:8bit,CMOS MCU 制造商:ROHM Semiconductor 功能描述:8-bit CMOS microcontroller |

| MSM80C85ARS | 制造商:OK International 功能描述: 制造商:Panasonic Industrial Company 功能描述:IC |

| MSM80C86A-10GS | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:16-Bit CMOS MICROPROCESSOR |

| MSM80C86A-10JS | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:16-Bit CMOS MICROPROCESSOR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。