- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45393 > MSM82C84A-2JS (LAPIS SEMICONDUCTOR CO LTD) OTHER CLOCK GENERATOR, PQCC20 PDF資料下載

參數(shù)資料

| 型號: | MSM82C84A-2JS |

| 廠商: | LAPIS SEMICONDUCTOR CO LTD |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | OTHER CLOCK GENERATOR, PQCC20 |

| 封裝: | 0.350 INCH, 1.27 MM PITCH, PLASTIC, QFJ-20 |

| 文件頁數(shù): | 17/19頁 |

| 文件大小: | 210K |

| 代理商: | MSM82C84A-2JS |

6/18

Semiconductor

MSM82C84A-2RS/GS/JS

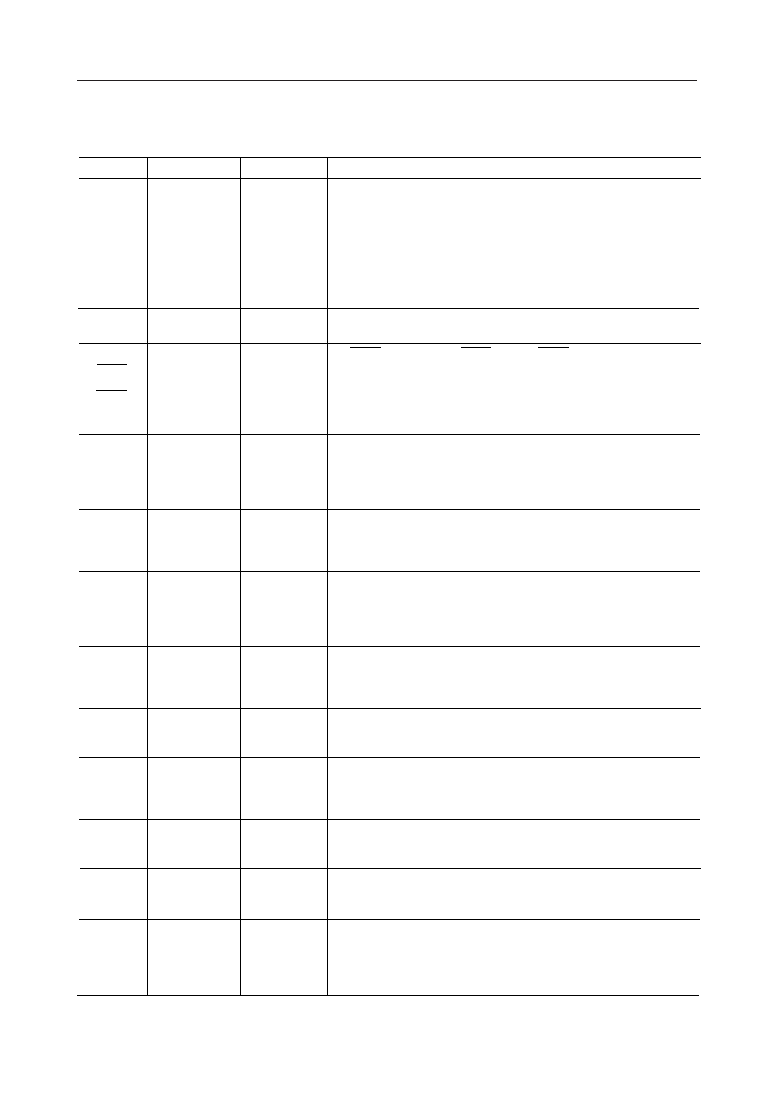

PIN DESCRIPTION

CSYNC

Name

Clock

Synchronization

Single

Input

Pin Symbol

Input/Output

Function

AEN1

AEN2

Address Enable

Signals

Input

RDY1

RDY2

Bus Ready

Signals

Input

READY

Ready Output

Output

CLK

Clock Output

Output

RES

Reset in

Input

Synchronizing signal for output of in-phase CLK signals when more

than one MSM82C84A-2 is used.

The internal counter is reset when this signal is at high level, and a

high level CLK output is generated. The internal counter is

subsequently activated and a 33% duty CLK output is generated when

this signal is switched to low level.

When this signal is used, external synchronization of EFI is necessary.

When the internal oscillator is used, it is necessary for this pin to be

kept to be low level.

PCLK

Output

This peripheral circuit clock signal is output in a 50% duty cycle at

a frequency half that of the clock signal.

The AEN1 signal enables RDY1, and the AEN2 signal RDY2.

The respective RDY inputs are activated when the level applied to

these pins is low.

Although two separate inputs are used in multi-master systems, only

the AEN which enables the RDY input to be used is to be switched to

low level in the case of not using multi-master systems.

Completion of data bus reading and writing by the device connected

to the system data bus is indicated when one of these signals is

switched to high level.

The relevant RDY input is enables only when the corresponding AEN

is at low level.

This signal is obtained by synchronizing the bus ready signal with

CLK.

This signal is output after guaranteeing the hold time for the

CPU in phase with the RDY input.

This signal is the clock used by the CPU and peripheral devices

connected to the CPU system data bus. The output waveform is

generated in a 33% duty cycle at a frequency 1/3 the oscillating

frequency of the crystal oscillator connected to the X1 and X2 pins,

or at a frequency 1/3 the EFI input frequency.

This low-level active input is used to generate a CPU reset signal.

Since a Schmitt trigger is included in the input circuit for this signal,

"power on resetting" can be achieved by connection of a simple RC

circuit.

RESET

Reset Output

Output

This signal is obtained by CLK synchronization of the input signal

applied to RES and is output in opposite phase to the RES input.

This signal is applied to the CPU as the system reset signal.

This signal selects the fundamental signal for generation of the CLK

signal. The CLK is generated from the crystal oscillator output when

this signal is at low level, and from the EFI input signal when at high

level.

The signal applied to this input pin generaters the CLK signal when

F/C is at high level. The frequency of the input signal needs to be

three times greater than the desired CLK frequency.

F/C

Clock Select

Signal

Input

OSC

Crystal

Resonator

Output

EFI

External Clock

Signal

Input

Peripheral Clock

Output

Crystal oscillator connections.

The crystal oscillator frequency needs to be three times greater than

the desired CLK frequency.

X1, X2

Crystal Oscillator

Connecting Pins

Input

Crystal oscillator output. This output frequency is the same as the

oscillating frequency of the oscillator connected to the X1 and X2

pins. As long as a Xtal oscillator is connected to the X1 and X2 pins,

this output signal can be obtained independently even if F/C is set to

high level to enable the EFI input to be used CLK generation purpose.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSM83C154-XXJS | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQCC44 |

| MSM83C154-1-XXJS | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQCC44 |

| MSM83C154S-XXXJS | 8-BIT, MROM, 24 MHz, MICROCONTROLLER, PQCC44 |

| MSM80C154SJS | 8-BIT, 24 MHz, MICROCONTROLLER, PQCC44 |

| MSM83C154S-XXXGS-2K | 8-BIT, MROM, 24 MHz, MICROCONTROLLER, PQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSM82C84A-2RS | 制造商:ROHM Semiconductor 功能描述:CLOCK GENERATOR AND DRIVER 制造商:ROHM Semiconductor 功能描述:Clock generator drive |

| MSM82C88-2GS | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:BUS CONTROLLER |

| MSM82C88-2JS | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:BUS CONTROLLER |

| MSM82C88-2RS | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:BUS CONTROLLER |

| MSM83C154S | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:CMOS 8-bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。