- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄45322 > MT80C51C-16D (ATMEL CORP) 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 PDF資料下載

參數(shù)資料

| 型號(hào): | MT80C51C-16D |

| 廠(chǎng)商: | ATMEL CORP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

| 封裝: | 1 MM HEIGHT, QFP-44 |

| 文件頁(yè)數(shù): | 127/170頁(yè) |

| 文件大小: | 4133K |

| 代理商: | MT80C51C-16D |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)當(dāng)前第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)

6

ATtiny4/5/9/10 [DATASHEET]

8127F–AVR–02/2013

4.

CPU Core

This section discusses the AVR core architecture in general. The main function of the CPU core is to ensure cor-

rect program execution. The CPU must therefore be able to access memories, perform calculations, control

peripherals, and handle interrupts.

4.1

Architectural Overview

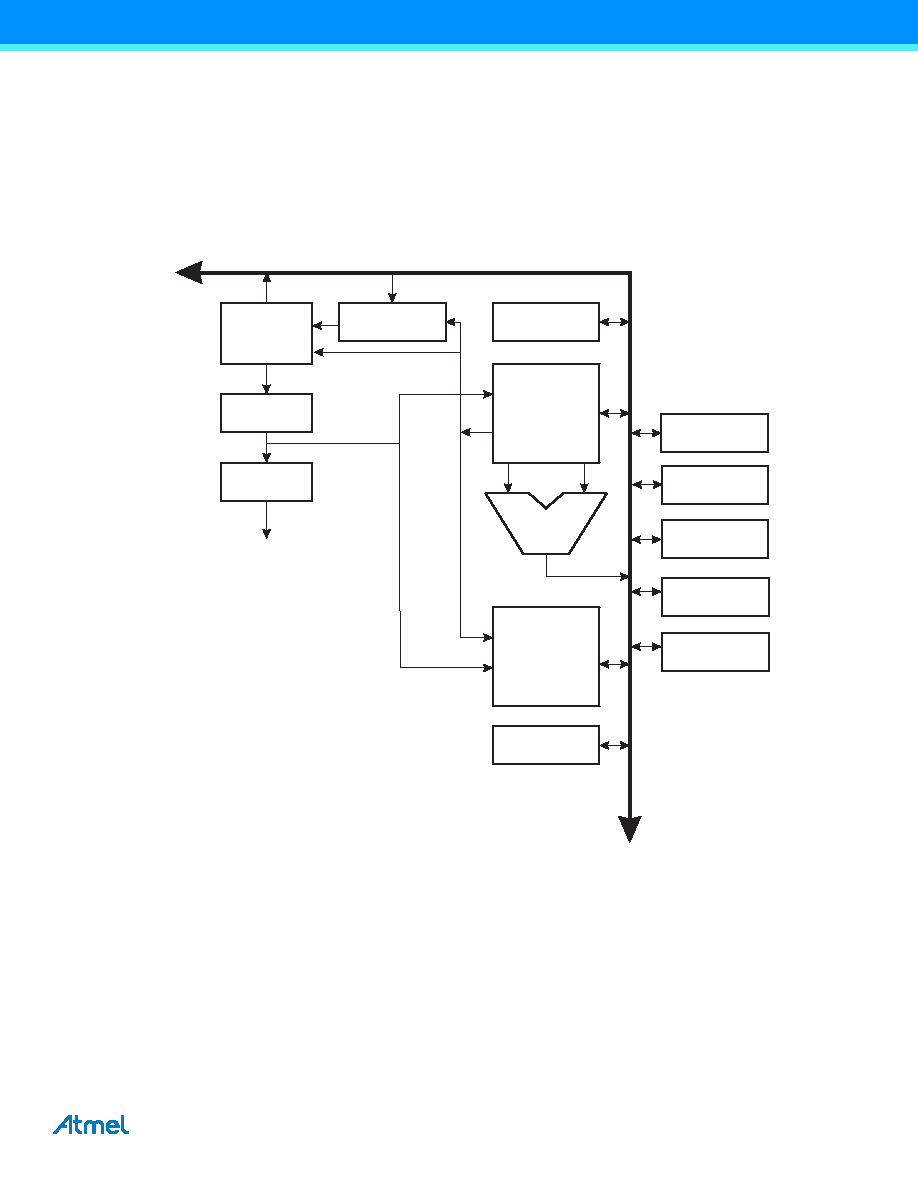

Figure 4-1.

Block Diagram of the AVR Architecture

In order to maximize performance and parallelism, the AVR uses a Harvard architecture – with separate memories

and buses for program and data. Instructions in the program memory are executed with a single level pipelining.

While one instruction is being executed, the next instruction is pre-fetched from the program memory. This concept

enables instructions to be executed in every clock cycle. The program memory is In-System reprogrammable

Flash memory.

The fast-access Register File contains 16 x 8-bit general purpose working registers with a single clock cycle

access time. This allows single-cycle Arithmetic Logic Unit (ALU) operation. In a typical ALU operation, two oper-

ands are output from the Register File, the operation is executed, and the result is stored back in the Register File

– in one clock cycle.

Flash

Program

Memory

Instruction

Register

Instruction

Decoder

Program

Counter

Control Lines

16 x 8

General

Purpose

Registrers

ALU

Status

and Control

I/O Lines

Data Bus 8-bit

Data

SRAM

Dir

ec

tA

ddr

essing

In

d

ir

e

ct

A

ddr

essing

Interrupt

Unit

Watchdog

Timer

Analog

Comparator

Timer/Counter 0

ADC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT80C51T-16D | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

| MF280C51T-36R | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, PQFP44 |

| MF280C51-36D | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, PQFP44 |

| MF180C51T-12D | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP44 |

| MV80C51C-20R | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, PQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT80C51FB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MT80C51FB/B | 制造商:Intel 功能描述: |

| MT80GB | 制造商:Datak Corporation 功能描述: |

| MT80JSF1G72NDY-1G1F1A2 | 制造商:Micron Technology Inc 功能描述:8GB 1GX72 DDR3 SDRAM MODULE PBF DIMM 1.5V REGISTERED - Trays |

| MT80KSF1G72NDY-1G4F1A3 | 制造商:Micron Technology Inc 功能描述:8GB 1GX72 DDR3 SDRAM MODULE PBF DIMM 1.35V FULLY BUFFERED - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。