- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359234 > MT90401 (Zarlink Semiconductor Inc.) SONET/SDH System Synchronizer PDF資料下載

參數(shù)資料

| 型號(hào): | MT90401 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | SONET/SDH System Synchronizer |

| 中文描述: | 的SONET / SDH系統(tǒng)的同步 |

| 文件頁(yè)數(shù): | 27/38頁(yè) |

| 文件大?。?/td> | 650K |

| 代理商: | MT90401 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)

MT90401

Data Sheet

27

Zarlink Semiconductor Inc.

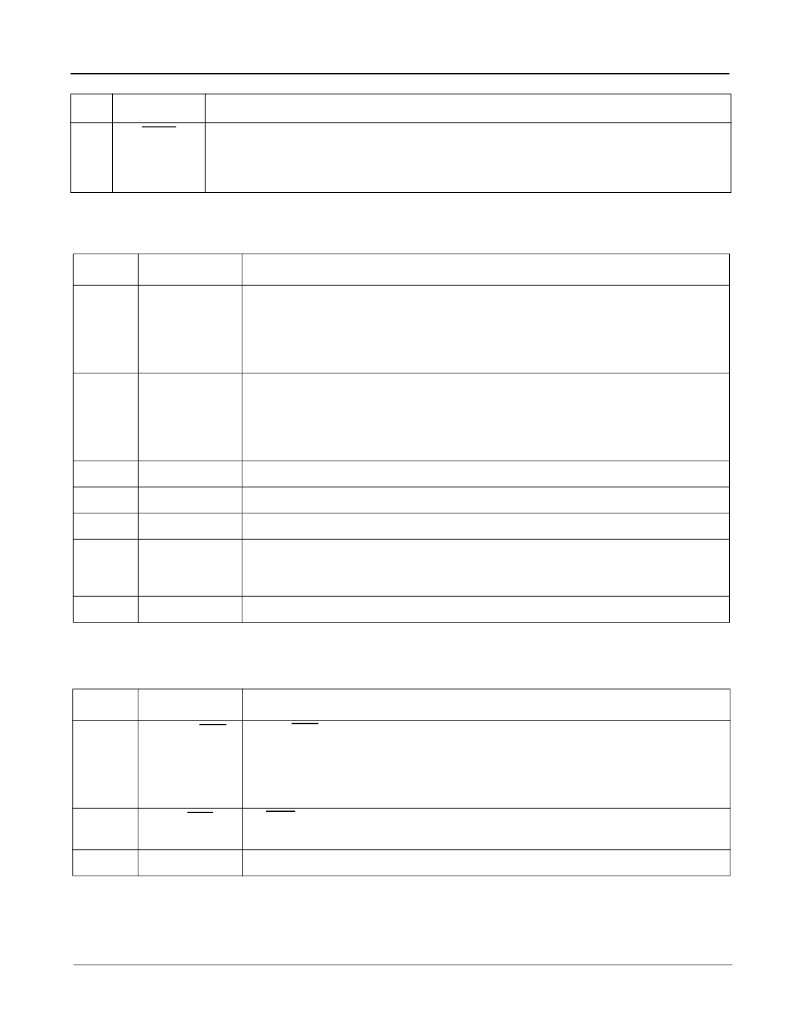

0

TCLR

TIE Clear

. Set to zero to clear the Time Interval Error correction circuit resulting in a

realignment of output phase with input phase. When this bit is zero, the Time Interval

Error correction circuit is disabled. When this bit is one, the Time Interval Error correction

circuit will function normally.

Bit

Name

Functional Description

7

PRIOOR

Primary Out Of Range

. A one indicates that the primary reference is off the PLL

center frequency by more than 12 ppm. The measurement is done on a 1 second

basis using a signal derived from the 20 MHz clock input on C20i. When the

accuracy of the 20 MHz clock is

±

4.6ppm, the effective out of range limits of the

PRIOOR signal will be

+

16.6 ppm to -7.4 ppm or +7.4 ppm to -16.6 ppm.

6

SECOOR

Secondary Out of Range

. A one indicates that the secondary reference is off the

PLL center frequency by more than 12 ppm. The measurement is done on a 1

second basis using a signal derived from the 20 MHz clock input on C20i. When the

accuracy of the 20 MHz clock is

±

4.6 ppm, the effective out of range limits of the

PRIOOR signal will be

+

16.6 ppm to -7.4 ppm or +7.4 ppm to -16.6 ppm.

5

LOCK

Lock

. This bit goes high when the PLL is in frequency lock to the input reference.

4

HOLDOVER

Holdover

. This bit goes high whenever the device is in Holdover mode.

3

RSV

Reserved.

2

FLim

Frequency Limit

. This bit goes high whenever the reference frequency hits the

input frequency offset tolerance of the PLL. This bit can flicker high in the event of

large excursions of still tolerable input jitter.

1-0

RSV

Reserved.

Table 7 - Status Register 1 (Address 01H - Read Only)

Bit

Name

Functional Description

7

E3DS3/OC3

E3DS3/OC3 Selection.

Set this bit to zero to enable the differential 155.52 MHz

output clock on the C155N/C155P pins and cause the C34/C44 pin to output its

nominal clock frequency divided by 4. Set this bit to one to disable the differential

155.52 MHz output clock on the C155N/C155P pins and cause the C34/C44 pin to

output its nominal clock frequency.

6

E3/DS3

E3/DS3.

Set this bit low to select a clock rate of 44.736 MHz for the C34/C44 pin.

Set high to select a clock rate of 34.368 MHz for the C34/C44 pins.

5-0

RSV

Reserved

. Set to zero for normal operation.

Table 8 - Control Register 2 (Address 04H - Read/Write)

Bit

Name

Functional Description

Table 6 - Control Register 1 (Address 00H - Read/Write) (continued)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT90401AB | 150MA LOW-DROPOUT VOLTAGE REGULATOR SO-8 PKG |

| MT90401AB1 | SONET/SDH System Synchronizer |

| MT9040 | T1/E1 Synchronizer |

| MT9040AN | T1/E1 Synchronizer |

| MT9043 | T1/E1 System Synchronizer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT90401AB | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:SONET/SDH System Synchronizer |

| MT90401AB1 | 制造商:Microsemi Corporation 功能描述:FRAMER SDH/SONET 3.3V 80LQFP EP - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SYNCHRONIZER SONET/SDH 80LQFP 制造商:Microsemi Corporation 功能描述:IC SYNCHRONIZER SONET/SDH 80LQFP |

| MT9040AN | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:T1/E1 Synchronizer |

| MT9040AN1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1 /T1 3.3V 48SSOP - Rail/Tube |

| MT9040ANR1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1 /T1 3.3V 48SSOP - Tape and Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。