- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383646 > MT9173AN (Mitel Networks Corporation) Digital Subscriber Interface Circuit with RxSB PDF資料下載

參數(shù)資料

| 型號: | MT9173AN |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | Digital Subscriber Interface Circuit with RxSB |

| 中文描述: | 數(shù)字用戶接口電路RxSB |

| 文件頁數(shù): | 11/22頁 |

| 文件大?。?/td> | 411K |

| 代理商: | MT9173AN |

Preliminary Information

MT9173/74

9-147

receiving signalling information and lower speed

data between the line and the system. In DN/DUAL

mode the DNIC receives a C-channel on CDSTi

while transmitting a C-channel on CDSTo.

F

ifteen

channel times later (halfway through the frame) a D-

channel is received on CDSTi while a D-channel is

transmitted on CDSTo. This is shown in Figure 7.

The order of the C and D bytes in DUAL port mode

can be reversed by the mode select pins. See Table

1 for a listing of the byte orientations.

The D-channel exists only in DN mode and may be

used for transferring low speed data or signalling

information over the line at 8, 16 or 64 kbit/s (by

using the DINB feature). The information passes

transparently through the DNIC and is transmitted to

or received from the line at the bit rate selected in the

Control Register.

If the bit rate is 80 kbit/s, only D0 is transmitted and

received. At 160 kbit/s, D0 and D1 are transmitted

and received. When the DINB bit is set in the Control

Register the entire D-channel is transmitted and

received in the B1-channel timeslot.

The C-channel is used for transferring control and

status information between the DNIC and the

system. The Control and Diagnostics Registers are

accessed through the C-channel. They contain

information to control the DNIC and carry out the

diagnostics as well as the HK bit to be transmitted on

the line as described in Tables 4 and 5. Bits 0 and 1

of the C-channel select between the Control and

Diagnostics Register. If these bits are 0, 0 then the

C-channel information is written to the Control

Register (Table 4). If they are 0, 1 the C-

c

hannel is

written to the Diagnostics Register (Table 5).

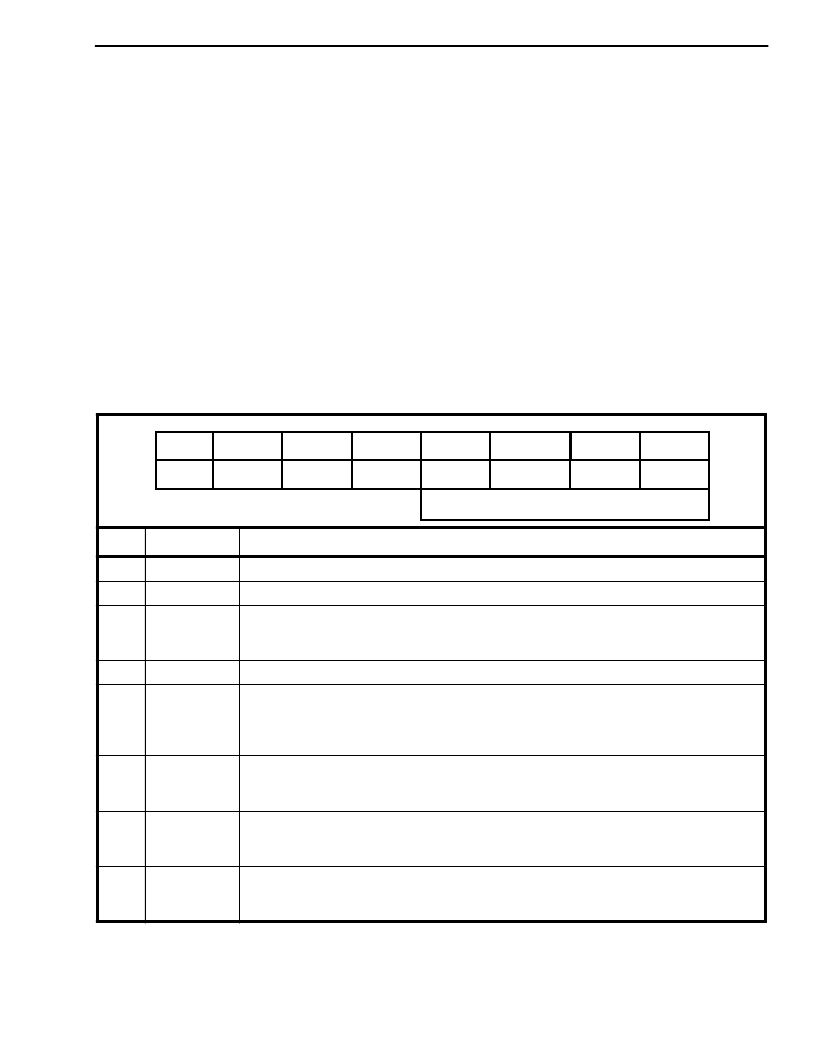

Table 4. Control Register

Notes:

Suggested use of ATTACK:

-At 160 kbit/s full convergence requires 850 ms with ATTACK held high for the first 240 frames or 30 ms.

-At 80 kbit/s full convergence requires 1.75 s with ATTACK held high for the first 480 frames or 60 ms.

When bits 4-7 of the Control Register are all set to one, the DNIC operates in one of the default modes as defined in Table 4a,

depending upon the status of bit-3.

Bit

Name

Description

0

Reg Sel-1

Register Select-1. Must be set to ’0’ to select the Control Register.

1

Reg Sel-2

Register Select-2. Must be set to ’0’ to select the Control Register.

2

DRR

Diagnostics Register Reset. Writing a "0" to this bit will cause a diagnostics register reset

to occur coincident with the next frame pulse as in the MT8972A. When this bit is a logic

"1", the Diagnostics Register will not be reset.

3

BRS

Bit Rate Select. When set to ’0’ selects 80 kbit/s. When set to ’1’, selects 160 kbit/s.

4

DINB

D-Channel in B Timeslot. When ’0’, the D-channel bits (D0 or D0 and D1) corresponding

to the selected bit rate (80 or 160 kbit/s) are transmitted during the normal D-channel bit

times. When set to ’1’, the entire D-channel (D0-D7) is transmitted during the B1-channel

timeslot on the line providing a 64 kbit/s D-channel link.

5

PSEN

Prescrambler/Deprescrambler Enable. When set to ’1’, the data prescrambler and

deprescrambler are enabled. When set to ’0’, the data prescrambler and deprescrambler

are disabled.

6

ATTACK

Convergence Speedup. When set to ’1’, the echo canceller will converge to the reflection

coefficient much faster. Used on power-up for fast convergence.

When ’0’, the echo

canceller will require the normal amount of time to converge to a reflection coefficient.

7

TxHK

Transmit Housekeeping. When set to ’0’, logic zero is transmitted over the line as

Housekeeping Bit. When set to ’1’, logic one is transmitted over the line as

Housekeeping Bit.

bit 0

bit 1

bit 2

bit 3

bit 4

bit 5

bit 6

bit 7

Reg Sel-1

Reg Sel-2

DRR

BRS

DINB

PSEN

ATTACK

TxHK

Default Mode Selection (Refer to Table 4a)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9173AP | Digital Subscriber Interface Circuit with RxSB |

| MT9173 | Digital Subscriber Interface Circuit with RxSB |

| MT9173 | Digital Subscriber Interface Circuit with RxSB(數(shù)字用戶接口電路(帶接收同步位)) |

| MT9174 | Digital Network Interface Circuit with RxSB(數(shù)字網(wǎng)絡(luò)接口電路(帶接收同步位)) |

| MT9196 | Integrated Digital Phone Circuit (IDPC)(集成數(shù)字電話電路) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9173AN1 | 制造商:Microsemi Corporation 功能描述:PB FREE DNIC 1.5UM 制造商:Microsemi Corporation 功能描述:DGTL INTRFC CIRCUIT 24SSOP - Rail/Tube 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SUBSCRIBER NETWRK DSIC 24SSOP 制造商:Microsemi Corporation 功能描述:IC SUBSCRIBER NETWRK DSIC 24SSOP |

| MT9173ANR1 | 制造商:Microsemi Corporation 功能描述:DGTL INTRFC CIRCUIT 24SSOP - Tape and Reel 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SUBSCRIBER NETWRK DSIC 24SSOP 制造商:Microsemi Corporation 功能描述:IC SUBSCRIBER NETWRK DSIC 24SSOP |

| MT9173AP | 制造商:Microsemi Corporation 功能描述:DGTL INTRFC CIRCUIT 28PLCC - Rail/Tube |

| MT9173AP1 | 制造商:Microsemi Corporation 功能描述:DGTL INTRFC CIRCUIT 28PLCC - Rail/Tube |

| MT9174 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO2-CMOS ST-BUS⑩ FAMILY Digital Network Interface Circuit with Receive Sync Marker Bit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。