- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383646 > MT91L60 (Mitel Networks Corporation) 3 Volt Multi-Featured Codec (MFC)(3V 多特性編解碼器) PDF資料下載

參數(shù)資料

| 型號: | MT91L60 |

| 廠商: | Mitel Networks Corporation |

| 元件分類: | Codec |

| 英文描述: | 3 Volt Multi-Featured Codec (MFC)(3V 多特性編解碼器) |

| 中文描述: | 3伏多精選編解碼器(MFC)中(3V的多特性編解碼器) |

| 文件頁數(shù): | 7/32頁 |

| 文件大小: | 146K |

| 代理商: | MT91L60 |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

Advance Information

MT91L60/61

7

When 0, D-Channel data is shifted at the rate of 2

bits/frame (16 kb/s default).

16 kb/s D-Channel operation is the default mode

which allows the microprocessor access to a full byte

of D-Channel information every fourth ST-BUS

frame. By arbitrarily assigning ST-BUS frame n as

the

reference

frame,

microprocessor D-Channel read and write operations

are performed, then:

during

which

the

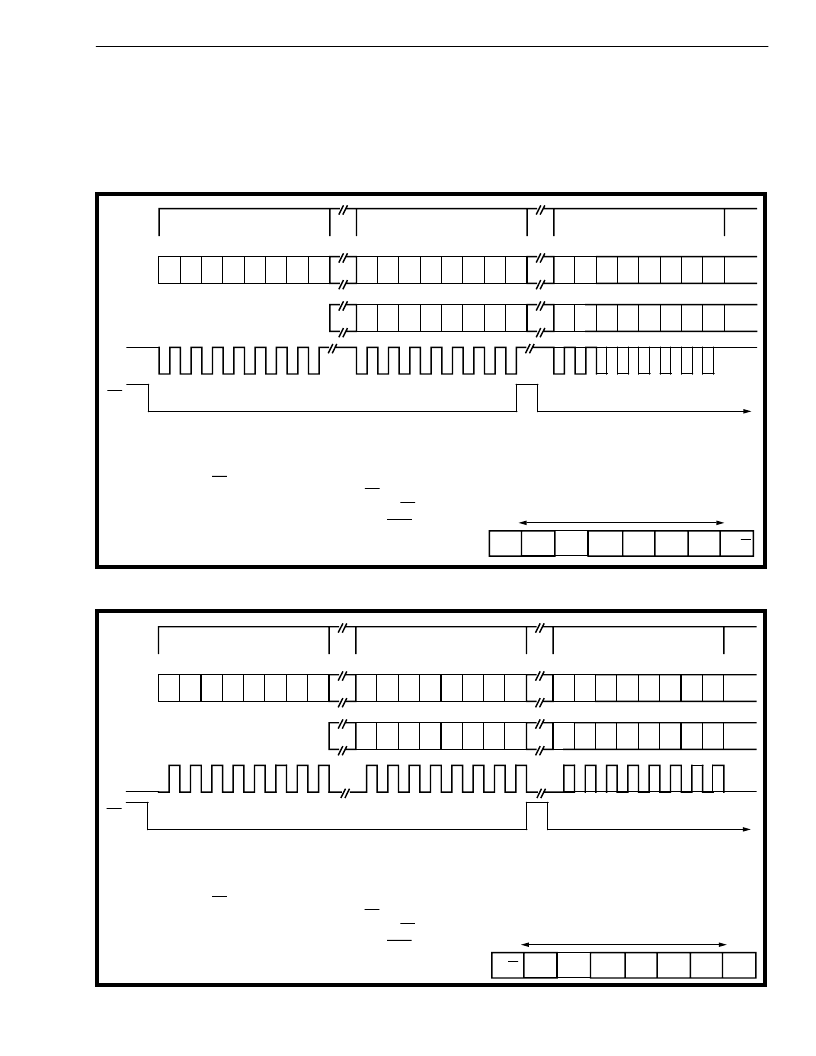

Figure 4 - Serial Port Relative Timing for Intel Mode 0

Figure 5 - Serial Port Relative Timing for Motorola Mode 00/National Microwire

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

X

X

A

2

A

1

A

0

R/W

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

Delays due to internal processor timing which are transparent.

The MT91L60/L61:latches received data on the rising edge of SCLK.

-outputs transmit data on the falling edge of SCLK.

y

The falling edge of CS indicates that a COMMAND/ADDRESS byte will be transmitted from the microprocessor. The

subsequent byte is always data until terminated via CS returning high.

A new COMMAND/ADDRESS byte may be loaded only by CS cycling high then low again.

The COMMAND/ADDRESS byte contains:

1 bit - Read/Write

3 bits - Addressing Data

4 bits - Unused

y

COMMAND/ADDRESS

DATA INPUT/OUTPUT

COMMAND/ADDRESS:

DATA 1

RECEIVE

DATA 1

TRANSMIT

SCLK

CS

D

7

D

0

X

X

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

y

COMMAND/ADDRESS

DATA INPUT/OUTPUT

COMMAND/ADDRESS:

DATA 2

RECEIVE

DATA 1

TRANSMIT

SCLK

CS

R/W

X

A

1

A

0

X

D

7

D

0

Delays due to internal processor timing which are transparent .

The MT91L60/L61: latches received data on the rising edge of SCLK.

-outputs transmit data on the falling edge of SCLK.

The falling edge of CS indicates that a COMMAND/ADDRESS byte will be transmitted from the microprocessor. The

subsequent byte is always data until terminated via CS returning high.

A new COMMAND/ADDRESS byte may be loaded only by CS cycling high then low again.

The COMMAND/ADDRESS byte contains:

1 bit - Read/Write

3 bits - Addressing Data

4 bits - Unused

y

X

X

A

2

相關PDF資料 |

PDF描述 |

|---|---|

| MT91L61 | 3 Volt Multi-Featured Codec (MFC)(3V 多特性編解碼器) |

| MT91L61 | ISO2-CMOS 3 Volt Multi-Featured Codec (MFC) |

| MT91L61AE | ISO2-CMOS 3 Volt Multi-Featured Codec (MFC) |

| MT91L61AN | ISO2-CMOS 3 Volt Multi-Featured Codec (MFC) |

| MT91L61AS | ISO2-CMOS 3 Volt Multi-Featured Codec (MFC) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MT91L60AE | 制造商:Microsemi Corporation 功能描述:MULTI-FEATURED CODEC 24PDIP - Rail/Tube |

| MT91L60AN | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:3 Volt Multi-Featured Codec (MFC) |

| MT91L60AS | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO2-CMOS 3 Volt Multi-Featured Codec (MFC) |

| MT91L60AS1 | 制造商:Microsemi Corporation 功能描述: |

| MT91L60ASR | 制造商:Microsemi Corporation 功能描述:MULTI-FEATURED CODEC 20SOIC W - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。