- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369943 > P83C562EBA (NXP Semiconductors N.V.) 8-BIT MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號: | P83C562EBA |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 8位微控制器 |

| 英文描述: | 8-BIT MICROCONTROLLER |

| 中文描述: | 8位微控制器 |

| 文件頁數(shù): | 17/52頁 |

| 文件大?。?/td> | 299K |

| 代理商: | P83C562EBA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

1997 Apr 08

17

Philips Semiconductors

Product specification

8-bit microcontroller

P83C562; P80C562

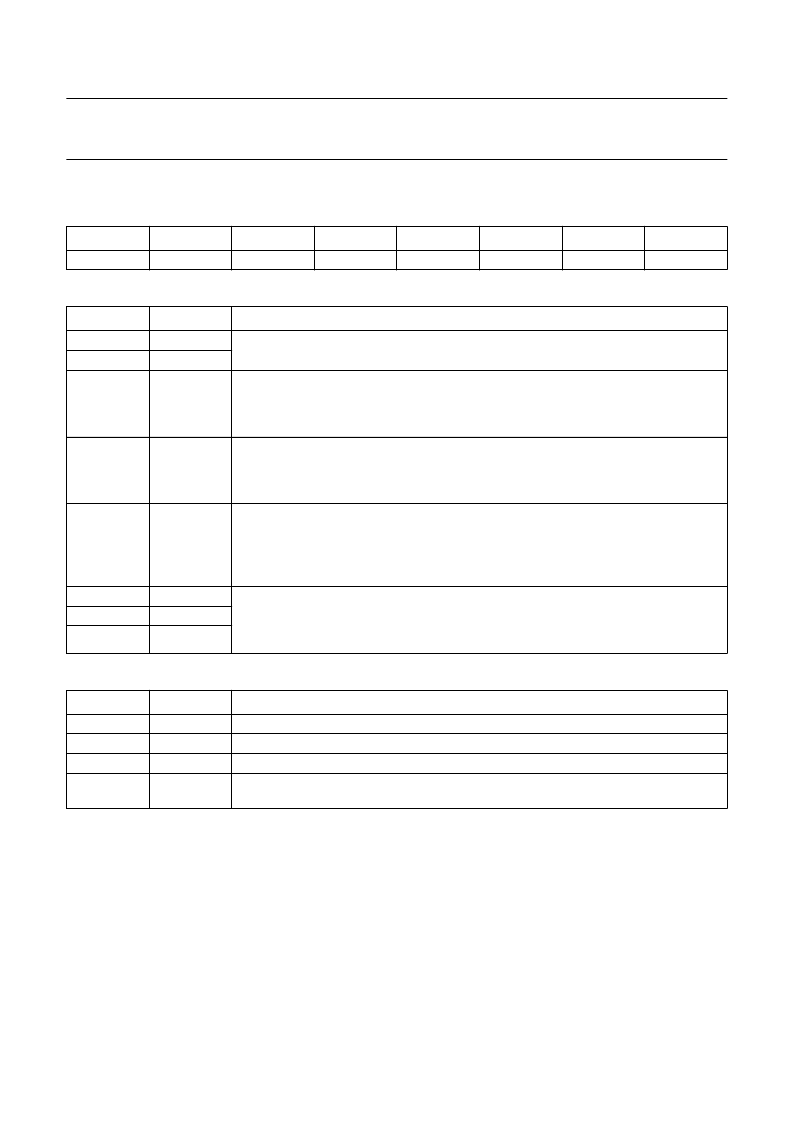

11.2

ADC Control Register (ADCON)

Table 9

ADC Control Register (SFR address C5H)

Table 10

Description of ADCON bits

Table 11

Function of ADCI and ADCS bits

7

6

5

4

3

2

1

0

ADEX

ADCI

ADCS

AADR2

AADR1

AADR0

BIT

SYMBOL

ADEX

DESCRIPTION

7

6

5

These two bits are reserved.

Enable external start:

start of conversion by STADC. If ADEX = 0, then conversion

can not be started externally by STADC (only by software by setting ADCS).

If ADEX = 1, then conversion can be started externally by a rising edge on STADC or by

software.

ADC interrupt flag:

this flag is set when an analog-to-digital conversion result is ready

to be read. An interrupt is invoked if it is enabled. The flag must be cleared by the

interrupt service routine. While this flag is set, the ADC cannot start a new conversion.

ADCI cannot be set by software.

ADC start and status:

setting this bit starts an ADC conversion. It may be set by

software or by the external signal STADC. The ADC logic ensures that this signal is

HIGH while the ADC is busy. On completion of the conversion, ADCS is reset

immediately after the interrupt flag has been set. ADCS can not be reset by software nor

can a new conversion be started if either ADCS or ADCI is HIGH.

Analog input select:

these three bits are used to select one of the eight analog inputs

of Port 5, for conversion. A selection can only be made when ADCI and ADCS are both

LOW. AADR2 is the most significant bit (e.g. 100 selects the ADC4 analog input

channel).

4

ADCI

3

ADCS

2

1

0

AADR.2

AADR.1

AADR.0

ADCI

ADCS

OPERATION

0

0

1

1

0

1

0

1

ADC not busy, a conversion can be started.

ADC busy, start of a new conversion is blocked.

Conversion completed; start of a new conversion is blocked.

Intermediate status for a maximum of one machine cycle before conversion is

completed.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P83C562EFA | 8-BIT MICROCONTROLLER |

| P80C562 | 8-BIT MICROCONTROLLER |

| P80C562EFA | 8-BIT MICROCONTROLLER |

| P83C562EHA | 8-BIT MICROCONTROLLER |

| P8212 | Light emitting/receiving module |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P83C562EBA/031 | 制造商:NXP Semiconductors 功能描述:Electronic Component |

| P83C562EBA/NNN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|8051 CPU|CMOS|LDCC|68PIN|PLASTIC |

| P83C562EFA | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller |

| P83C562EFA/NNN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|8051 CPU|CMOS|LDCC|68PIN|PLASTIC |

| P83C562EHA | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。