- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367804 > PCA1070P (NXP SEMICONDUCTORS) Multistandard programmable analog CMOS transmission IC PDF資料下載

參數(shù)資料

| 型號(hào): | PCA1070P |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Multistandard programmable analog CMOS transmission IC |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PDIP24 |

| 文件頁數(shù): | 25/36頁 |

| 文件大小: | 180K |

| 代理商: | PCA1070P |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

1997 Jun 20

25

Philips Semiconductors

Product specification

Multistandard programmable analog

CMOS transmission IC

PCA1070

Notes

1.

Time needed to reach at start-up the default DC voltage V

SLPE

(

±

10% from its final value):

a) Time depends strongly on the value of the capacitor(s) at V

DD

and VMC; with a lower value of C

VDD

the DC

start-up time decreases.

b) The start-up time can be reduced considerably by programming the bit code DST = 1 during the start-up

procedure. In practice this is possible as soon as the microcontroller has become operational.

Time needed to reach the DC voltage V

SLPE

within

±

10% from its final value) after reprogramming VDCx.

The supply voltage V

DD

is determined by the regulated DC voltage at pin SLPE and by the voltage drop between

pin SLPE and V

DD

; see Chapter “Functional description”.

Relaxed performance means: parameters can deviate from their specified values.

Rejection between supply pin V

DD

and V

P

. Rejection between pin LN and V

P

can be calculated by adding the

attenuation of the first-order low-pass filter (R = 250

, C = 150

μ

F) between SLPE and V

DD

.

If V

DD

is above this level, the default values have been loaded into the internal registers.

RMC changes from logic 1 to logic 0 when voltage on pin VMC is increasing; RMC changes from logic 0 to logic 1

when voltage on pin VMC is decreasing; see Fig.4.

Common mode signal is applied via 2

×

470

external resistors connected to pins MIC+ and MIC

.

Not tested, guaranteed by design.

10. Time needed to reach default settings (

±

3 dB).

11. At low gain settings the confidence tone gain will be slightly higher than the specified value due to a residual signal.

12. G

CTA

, the confidence tone gain for asymmetrical drive, equals G

CTS

6 (in dB).

13. To be left open-circuit in application.

14. The AC set impedance between pin LN and V

SS

consists of R

a

+ (R

b

// C) in parallel with an artificial inductor L

eq

and

internal resistors R

p

and R

LSI

and internal capacitor C

p

. See Chapter “Functional description”.

15. Balance Return Loss indicates the deviation of an impedance with respect to a reference impedance.

BRL = 20 log

(Z

LN

+ Z

ref

)/(Z

LN

Z

ref

)

where Z

LN

≈

R

a

+ (R

b

// C) is the impedance seen into pin LN

Z

ref

= R

a(ref)

+ (R

b(ref)

// C

ref

) is the reference impedance.

16. Without clock the set impedance is automatically set to Z

set

= 600

(typical).

17. The combination R

a

= 0 and R

b

= 0 is not allowed (see Tables 9 and 10, note 1).

18. Value logic 0 can also be programmed.

19. Value f

p

= 12 kHz can also be programmed.

20. Attack and release times are also valid under low current and voltage conditions.

21. G

RA

, the receiving channel gain for asymmetrical drive equals G

RS

6 (in dB).

22. The maximum possible output swing depends on the DC conditions (the programmed voltage V

SLPE

and the load on

the supply pin V

DD

) and on the gain setting of the receiving channel.

2.

3.

4.

5.

6.

7.

8.

9.

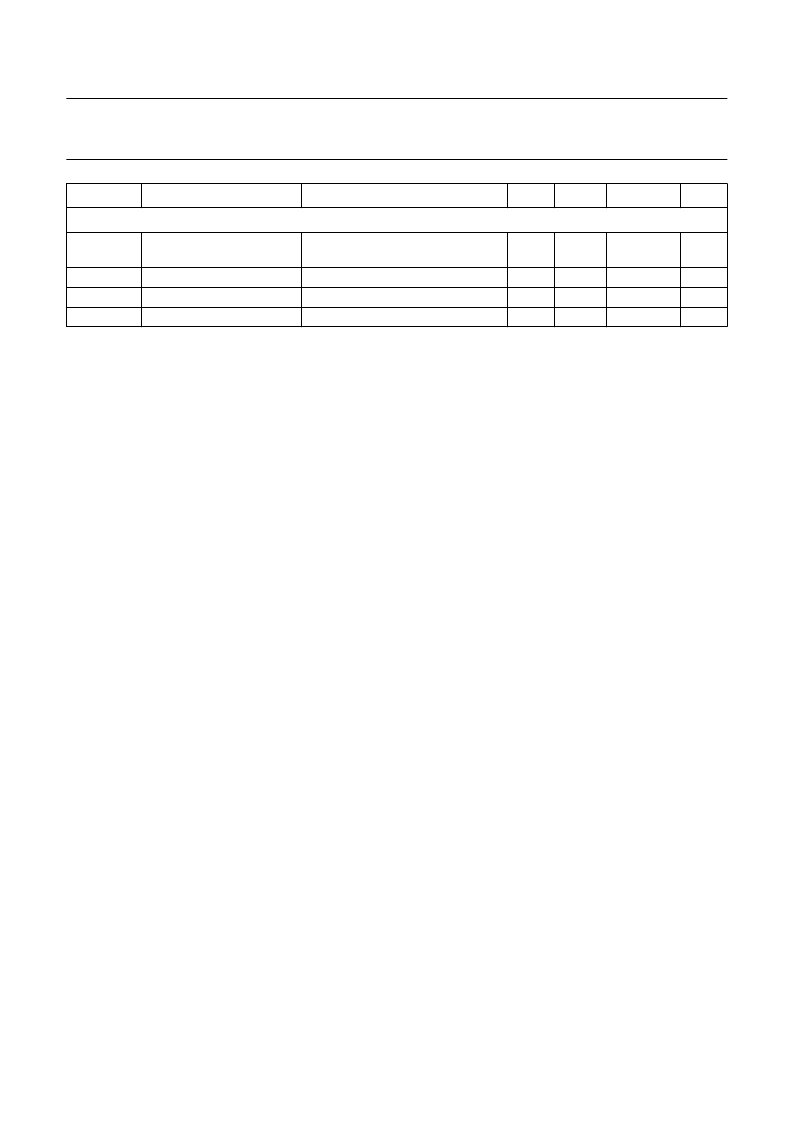

Clock input: CLK

v

CLK(p-p)

input signal voltage level

(peak-to-peak value)

frequency tolerance

input series resistance

input series capacitance

200

V

VMC

V

SS

mV

f

CLK

/f

CLK

R

CLK

C

CLK

note 29

800

4

±

0.5

%

k

pF

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCA1070T | Multistandard programmable analog CMOS transmission IC |

| PCA145LA | Optoelectronic |

| PCA145LCA | Optoelectronic |

| PCA145LG | Optoelectronic |

| PCA145LR | Optoelectronic |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCA1070T | 制造商:NXP Semiconductors 功能描述: |

| PCA-107-18-086 | 制造商:Power Dynamics Inc 功能描述:PCA Series Power Entry Module |

| PCA-1-08-HU-3-50 | 功能描述:FFC & FPC連接器 8P R/A UPPER CONTACTS RoHS:否 制造商:JAE Electronics 產(chǎn)品類型:Plugs 系列:HD 節(jié)距:0.5 mm 位置/觸點(diǎn)數(shù)量:40 安裝角: 安裝風(fēng)格:Cable 外殼材料:Plastic 觸點(diǎn)材料:Copper Alloy 觸點(diǎn)電鍍:Gold 電壓額定值:100 V per contact 電流額定值:0.24 A to 1 A |

| PCA-1-08-V-3-20 | 功能描述:FFC & FPC連接器 8P TOP ENTRY THRU HOLE RoHS:否 制造商:JAE Electronics 產(chǎn)品類型:Plugs 系列:HD 節(jié)距:0.5 mm 位置/觸點(diǎn)數(shù)量:40 安裝角: 安裝風(fēng)格:Cable 外殼材料:Plastic 觸點(diǎn)材料:Copper Alloy 觸點(diǎn)電鍍:Gold 電壓額定值:100 V per contact 電流額定值:0.24 A to 1 A |

| PCA11 0-9 | 制造商:Panduit Corp 功能描述:Clip-On Wire Markers, .11"-.13" Wire OD, Black/White 300 PC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。