- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367822 > PCK2000 (NXP Semiconductors N.V.) CK97 (66/100MHz) System Clock Generator(CK97 (66/100MHz) 系統(tǒng)時(shí)鐘發(fā)生器) PDF資料下載

參數(shù)資料

| 型號(hào): | PCK2000 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | CK97 (66/100MHz) System Clock Generator(CK97 (66/100MHz) 系統(tǒng)時(shí)鐘發(fā)生器) |

| 中文描述: | CK97(66/100MHz)系統(tǒng)時(shí)鐘發(fā)生器(CK97(66/100MHz)系統(tǒng)時(shí)鐘發(fā)生器) |

| 文件頁數(shù): | 4/14頁 |

| 文件大小: | 90K |

| 代理商: | PCK2000 |

Philips Semiconductors

Product specification

PCK2000

CK97 (66/100MHz) System Clock Generator

1998 Sep 29

4

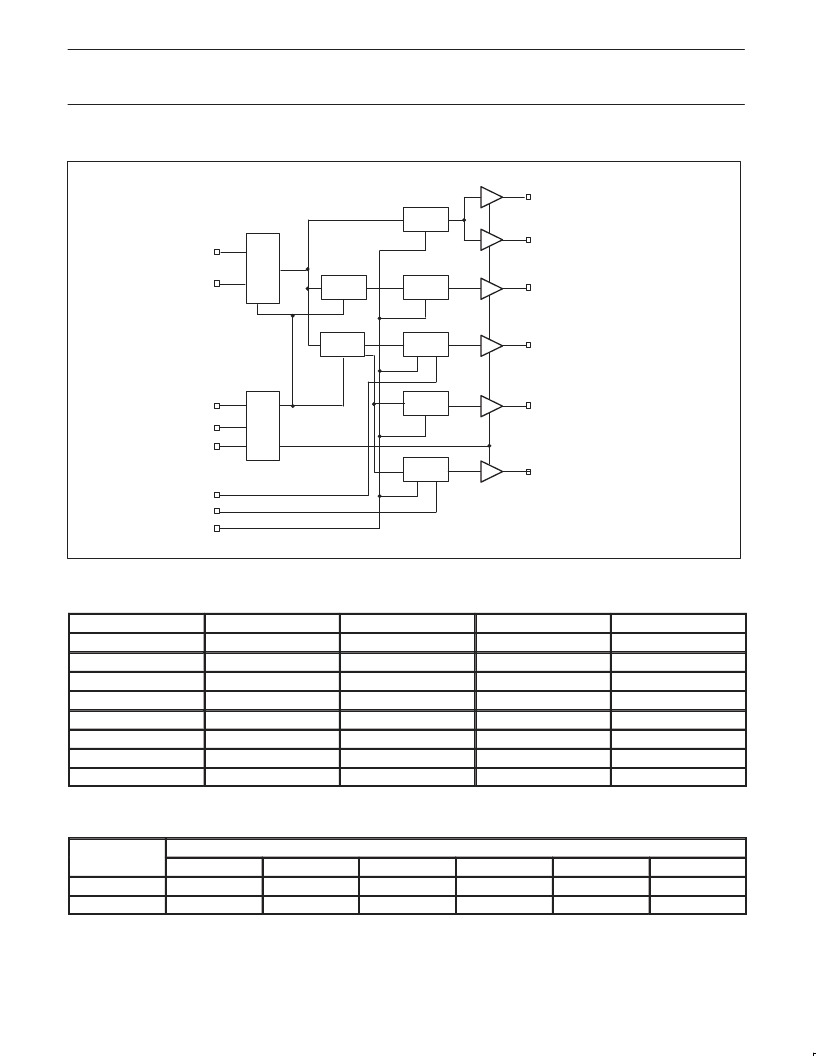

BLOCK DIAGRAM

PWRDWN

LOGIC

PWRDWN

LOGIC

STOP

LOGIC

STOP

LOGIC

PLL1

PLL2

14.318

MHZ

OSC

PWRDWN

LOGIC

LOGIC

SW00236

X

X

X

X

X

X

X

X

X

X

X

X

X

X

REFCLK [0–2](14.318 MHz)

PWRDWN

PCISTOP

CPUSTOP

SEL0

SEL1

SEL100/66

XTAL_IN

XTAL_OUT

IOAPIC [0–1](14.318 MHz)

48MHz [0–1](48MHz)

CPUCLK [0–3] (100MHz/66MHz)

PCICLK_F (33MHz)

PCICLK [1–7](33MHz)

SELECT FUNCTIONS

SEL100/66

SEL1

SEL0

FUNCTION

NOTES

0

0

0

TRI-State

1

0

0

1

Reserved

0

1

0

Reserved

0

1

1

Active 66MHz

1

0

0

Test mode

1

1

0

1

Reserved

1

1

0

Reserved

1

1

1

Active 100MHz

NOTE:

1. Internal decode logic for all three select inputs implemented.

FUNCTION

DESCRIPTION

OUTPUTS

CPU

PCI, PCI_F

48MHz

REF

IOAPIC

NOTES

3-STATE

HI-Z

HI-Z

HI-Z

HI-Z

HI-Z

TEST MODE

TCLK/2

TCLK/6

TCLK/2

TCLK

TCLK

NOTE:

1. TCLK is a test clock driven in on the XTAL_IN input in Test Mode.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCK2000DL | CK97 66/100MHz System Clock Generator |

| PCK2001M | 14.318-150 MHz IIC 1:10 clock buffer(14.318-150 MHz IIC 1:10時(shí)鐘緩沖器) |

| PCK2001R | 14.318-133 MHz I2C 1:6 Clock Buffer(14.318-133 MHz I2C 1:6時(shí)鐘緩沖器) |

| PCK2001 | 14.318-150 MHz I 2 C 1:18 Clock Buffer(14.318-150 MHz IIC 1:18時(shí)鐘緩沖器) |

| PCK2010RDL | CONN 622-5030 T&B |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCK2000DL | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CK97 66/100MHz System Clock Generator |

| PCK2000DL-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CPU System Clock Generator |

| PCK2000M | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CK97 66/100MHz Mobile System Clock Generator |

| PCK2000MDB | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CK97 66/100MHz Mobile System Clock Generator |

| PCK2000MDB-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CPU System Clock Generator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。