- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369960 > PDI1394P11BD (NXP SEMICONDUCTORS) 3-port physical layer interface PDF資料下載

參數(shù)資料

| 型號(hào): | PDI1394P11BD |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通用總線功能 |

| 英文描述: | 3-port physical layer interface |

| 中文描述: | TRIPLE LINE TRANSCEIVER, PQFP64 |

| 文件頁數(shù): | 13/42頁 |

| 文件大小: | 233K |

| 代理商: | PDI1394P11BD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Philips Semiconductors

Preliminary data

PDI1394P23

2-port/1-port 400 Mbps physical layer interface

2001 Sep 06

13

12.0

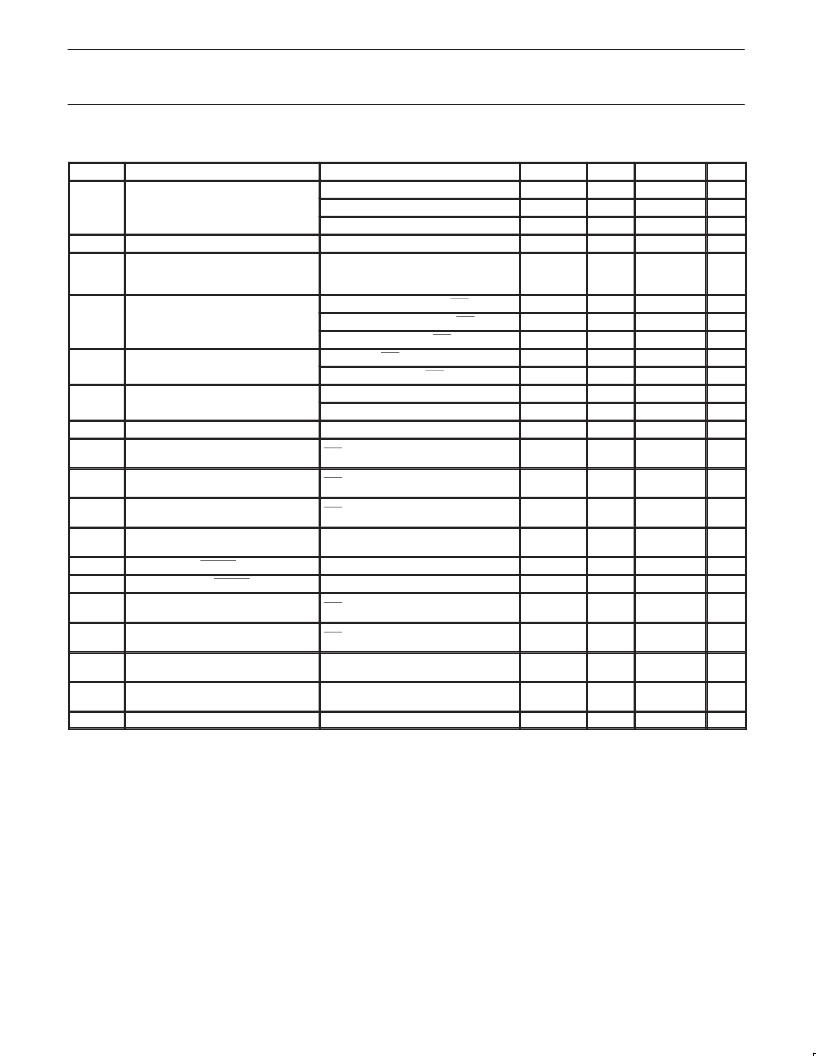

OTHER DEVICE I/O

SYMBOL

PARAMETER

TEST CONDITION

MIN

—

TYP

81

MAX

—

UNIT

mA

See Note 1

I

DD

Supply current

See Note 2

—

56

—

mA

See Note 3

—

50

—

mA

μ

A

I

DD–PD

Supply current in power down mode

PD = V

DD

in power down mode

390 k

resistor between cable power

and CPS pin: Measured at cable power

side of resistor

—

150

—

V

TH

Cable power status threshold voltage

4.7

—

7.5

V

Hi h l

High-level output voltage, pins CTL0,

CTL1, D0–D7, SYSCLK, CNA

CTL1, D0 D7, SYSCLK, CNA

V

DD

= 2.7 V, I

OH

= –4 mA, ISO = V

DD

V

DD

>= 3.0 V, I

OH

= –4 mA, ISO = V

DD

Annex J: I

OH

= –9 mA, ISO = 0

I

OL

= 4 mA, ISO = V

DD

Annex J: I

OL

= 9 mA, ISO = 0

V

DD

= 2.7 V, I

OH

= –4 mA; See Note 4

V

DD

>= 3.0 V, I

OH

= –4 mA; See Note 4

V

DD

= 2.7 V, I

OL

= 4 mA; See Note 4

2.4

—

—

V

V

OH

2.8

—

—

V

V

DD

–0.4

—

—

—

V

V

OL

Low-level output voltag ,

CTL1, D0–D7, CNA, SYSCLK

—

0.4

V

,

—

—

0.4

V

V

OH

High level output voltage pin C/LKON

High-level output voltage, pin C/LKON

2.4

—

—

V

2.7

—

—

V

V

OL

Low-level output voltage, pin C/LKON

—

—

0.3

V

I

BH+

Positive peak bus holder current, pins

CTL0, CTL1, D0–D7, LREQ

Negative peak bus holder current, pins

CTL0, CTL1, D0–D7, LREQ

Input current, pins LREQ, LPS, PD,

TEST0, BRIDGE, PC0–PC2

Off-state current, pins CTL0, CTL1,

D0–D7, C/LKON

Pullup current, RESET input

ISO = V

DD

, V

I

= 0 V to V

DD

0.05

—

1.0

mA

I

BH–

ISO = V

DD

, V

I

= 0 V to V

DD

–1.0

—

–0.05

mA

I

I

ISO = 0 V; V

DD

= 3.6 V

—

—

5

μ

A

I

OZ

VO = V

DD

or 0 V

–5

—

5

μ

A

I

RST-UP

I

RST-DN

V

I

= 1.5 V or 0 V

V

I

= V

DD

, PD = V

DD

–90

—

–20

μ

A

mA

Pulldown current, RESET input

.4

1.6

2.8

V

IT+

Positive going threshold voltage, LREQ,

CTL0, CTL1, D0–D7 inputs

Negative going threshold voltage, LREQ,

CTL0, CTL1, D0–D7 inputs

Positive going threshold voltage, LPS

inputs

Negative going threshold voltage, LPS

inputs

TPBIAS output voltage

ISO = 0 V

V

DD

/2 + 0.3

—

V

DD

/2 + 0.9

V

V

IT–

ISO = 0 V

V

DD

/2 – 0.9

—

V

DD

/2 – 0.3

V

V

LIT+

V

LREF

= 0.42 x V

DD

—

—

V

LREF

+1

V

V

LIT–

V

LREF

= 0.42 x V

DD

V

LREF

+0.2

—

—

V

V

O

NOTES:

1. Transmit Max Packet (2 ports transmitting max size isochronous packet (4096 bytes), sent on every isochronous interval, S400, data value

of 0xCCCCCCCCh), V

DD

= 3.3 V, T

= 25

°

C

2. Repeat typical packet (1 port receiving DV packets on every isochronous interval, 1 port repeating the packet, S100), V

DD

= 3.3 V,

TA = 25

°

C

3. Idle (receive cycle start on one port, transmit cycle start on other port) V

DD

= 3.3 V, T

A

= 25

°

C

4. The C/LKON pin is able to drive an isolation circuit according to Figure 5A-20 of the IEEE-1394a-2000 standard.

At rated I

O

current

1.665

—

2.015

V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PDI1394P25 | 1-port 400 Mbps physical layer interface |

| PDI1394P25BD | 1-port 400 Mbps physical layer interface |

| PDI1394P25EC | 1-port 400 Mbps physical layer interface |

| PDI1394P23BD | 2-port/1-port 400 Mbps physical layer interface |

| PDI1394L41BE | 8358 PBGA ENCRP NO-PB |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PDI1394P11BD-S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Transceiver |

| PDI1394P21 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3-port physical layer interface |

| PDI1394P21BE | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3-port physical layer interface |

| PDI1394P22 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3-port physical layer interface |

| PDI1394P22BD | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3-port physical layer interface |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。