- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367861 > PDM41024LA12TSO (Electronic Theatre Controls, Inc.) 1 Megabit Static RAM 128K x 8-Bit PDF資料下載

參數(shù)資料

| 型號: | PDM41024LA12TSO |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 1 Megabit Static RAM 128K x 8-Bit |

| 中文描述: | 1兆位靜態(tài)RAM 128K的× 8位 |

| 文件頁數(shù): | 5/8頁 |

| 文件大小: | 187K |

| 代理商: | PDM41024LA12TSO |

PDM41024

Rev. 3.3 - 4/09/98

5

1

2

3

4

5

6

7

8

9

10

11

12

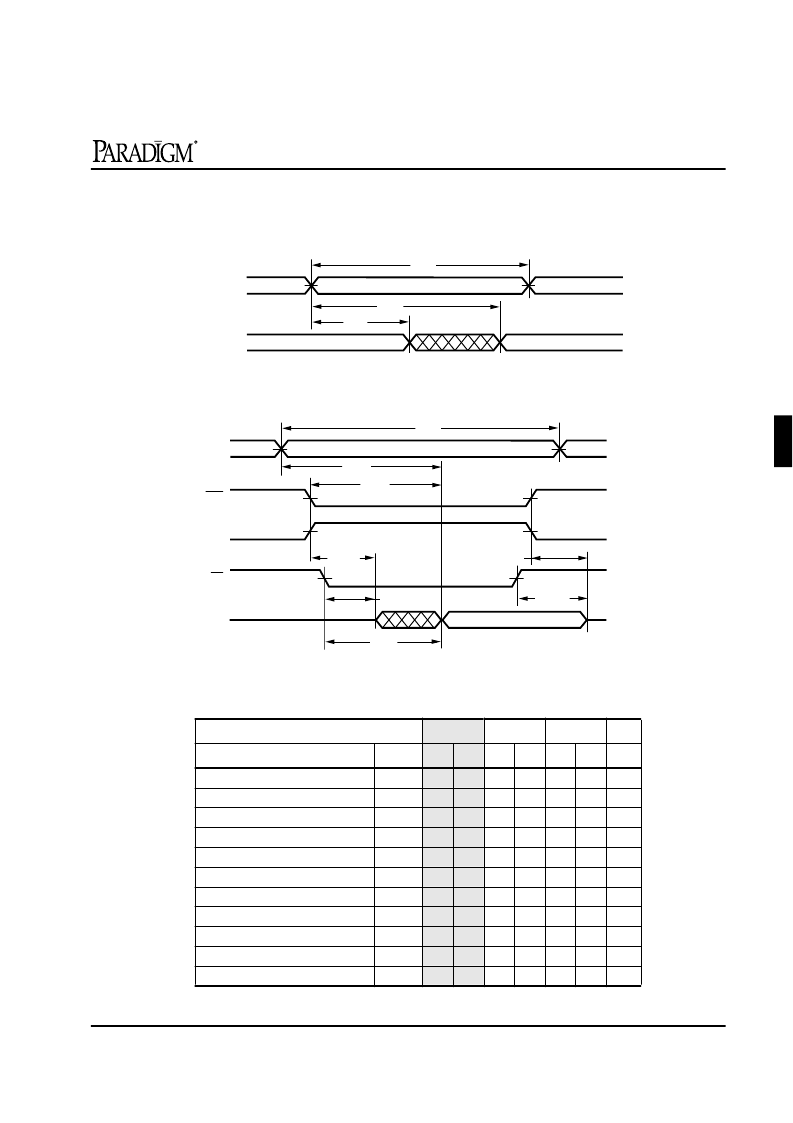

t

RC

t

ACE

t

AA

t

LZCE

t

HZCE

t

LZOE

t

HZOE

t

AOE

ADDR

CE1

CE2

OE

D

OUT

DATA VALID

Read Cycle No. 1

(4, 5)

Read Cycle No. 2

(2, 4, 6)

AC Electrical Characteristics

SHADED AREA = PRELIMINARY DATA

Notes referenced are after Data Retention Table.

Description

-10

(7)

-12

(7)

-15

READ Cycle

Sym

Min. Max. Min. Max. Min. Max. Units

READ cycle time

t

RC

10

12

15

ns

Address access time

t

AA

10

12

15

ns

Chip enable access time

t

ACE

10

12

15

ns

Output hold from address change

t

OH

3

3

3

ns

Chip enable to output in low Z

(1,3)

t

LZCE

5

5

5

ns

Chip disable to output in high Z

(1,2,3)

t

HZCE

6

6

7

ns

Chip enable to power up time

(3)

t

PU

0

0

0

ns

Chip disable to power down time

(3)

t

PD

10

12

15

ns

Output enable access time

t

AOE

6

6

6

ns

Output enable to output in low Z

(1,3)

t

LZOE

0

0

0

ns

Output disable to output in high Z

(1,3)

t

HZOE

6

6

6

ns

t

RC

t

AA

t

OH

PREVIOUS DATA VALID

DOUT

ADDR

DATA VALID

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。