- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367908 > PEEL22LV10AZS-35 (Electronic Theatre Controls, Inc.) CMOS Programmable Electrically Erasable Logic Device PDF資料下載

參數(shù)資料

| 型號(hào): | PEEL22LV10AZS-35 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | CMOS Programmable Electrically Erasable Logic Device |

| 中文描述: | 的CMOS電可擦除可編程邏輯器件 |

| 文件頁(yè)數(shù): | 5/10頁(yè) |

| 文件大小: | 146K |

| 代理商: | PEEL22LV10AZS-35 |

5

PEEL

TM

22LV10AZ

04-02-037D

Programmable Clock Options

(see Table 1)

A unique feature of the PEEL22LV10AZ is a

programmable clock multiplexer that allows the user to

select true or complement forms of either input pin or

product-term clock sources.

Operates in both 3 Volt and 3.3 Volt Systems

The PEEL22LV10AZ is designed to operate with a V

CC

range of 2.7 to 3.6 Volts D.C. This allows operation in

both 3 Volt 10% (battery operated) and 3.3 Volt 10%

(power supply operated) systems. The propagation

delay t

PD

is 5 ns slower at the lower voltage, but this is

typically not an issue in battery-operated systems (see

Table 6 - A.C. Electrical Characteristics).

Zero Power Feature

The CMOS PEEL22LV10AZ features "Zero-Power"

standby operation for ultra-low power consumption.

With the "Zero-Power" feature, transition-detection

circuitry monitors the inputs, I/Os (including CLK) and

feedbacks. If these signals do not change for a period

of time greater than approximately two t

PD

's, the outputs

are latched in their current state and the device

automatically powers down. When the next signal

transition is detected, the device will "wake up" for

active operation until the signals stop switching long

enough to trigger the next power-down. (Note that the

t

PD

is approximately 5 ns. slower on the first transition

from sleep mode.)

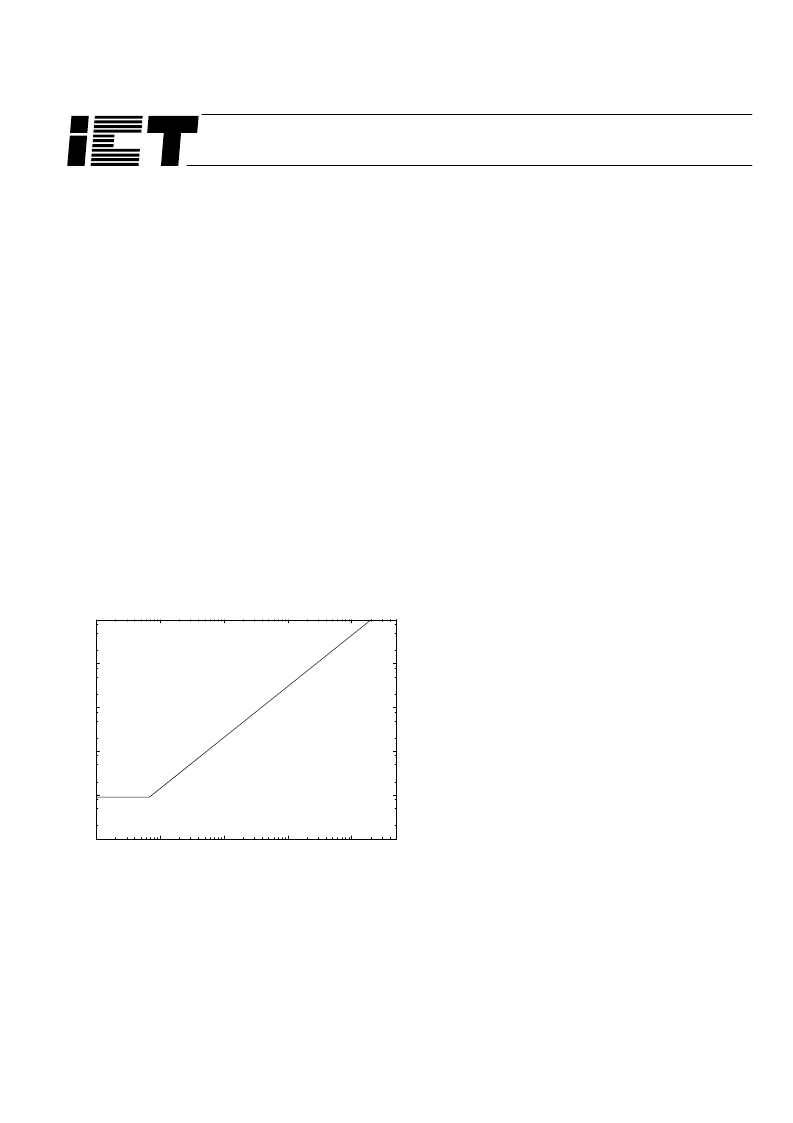

0.001

0.01

0.1

1

10

100

0.001

0.01

0.1

1

10

I

Frequency in MHz

Figure 5 - Typical ICC vs. Input Clock Frequency for

the 22LV10AZ

As a result of the "Zero-Power" feature, significant

power savings can be realized for combinatorial or

sequential operations when the inputs or clock change

at a modest rate. See Figure 5.

When the PEEL22LV10AZ is powered up, a built-in

feature holds the outputs in tri-state until V

CC

reaches

2.2V. This prevents output transitions during power-up.

Schmitt Trigger Inputs

The PEEL22LV10AZ has Schmitt trigger input buffers

on all inputs, including the clock. Schmitt trigger inputs

allow direct input of slow signals such as biomedical

and sine waves or clocks. They are also useful in

cleaning

up

noisy

signals.

PEEL22LV10AZ

especially

applications where the environment is less predictable.

This

makes

in

the

desirable

portable

Design Security

The PEEL22LV10AZ provides a special EEPROM

security bit that prevents unauthorized reading or

copying of designs programmed into the device. The

security bit is set by the PLD programmer, either at the

conclusion of the programming cycle or as a separate

step, after the device has been programmed. Once the

security bit is set it is impossible to verify (read) or

program the PEEL until the entire device has first been

erased with the bulk-erase function.

Signature Word

The signature word feature allows a 64-bit code to be

programmed into the PEEL22LV10AZ if the PEEL

V10A+ software option (see Table 1) is used. The code

can be read back even after the security bit has been

set. The signature word can be used to identify the

pattern programmed into the device or to record the

design revision, etc.

Programming Support

ICT's JEDEC file translator allows easy conversion of

existing 24 pin PLD designs to the PEEL22LV10AZ,

without the need for redesign. ICT supports a broad

range of popular third party design entry systems,

including Data I/O Synario and Abel, Logical Devices

CUPL and others. ICT also offers its proprietary

WinPLACE software, an easy-to-use entry level PC-

based software development system.

Programming support includes all the popular third

party programmers; Data I/O, Logical Devices, and

numerous others.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PEEL22LV10AZSI-25 | CMOS Programmable Electrically Erasable Logic Device |

| PEEL22LV10AZT-35 | CMOS Programmable Electrically Erasable Logic Device |

| PEEL22LV10AZTI-25 | CMOS Programmable Electrically Erasable Logic Device |

| pentium III | pentium III Processor for the PGA370 Socket at 500MHz to 933MHz(工作頻率500到933兆赫茲活動(dòng)帶PGA370插孔奔III處理器) |

| pentium II | pentium II processor With On-die Cache Mobile Module Connector 1 (MMC-1)(帶緩存和連接器1的奔II處理器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PEEL22LV10AZSI-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS Programmable Electrically Erasable Logic Device |

| PEEL22LV10AZSI-35 | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 12 INP 10 I/O 35ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| PEEL22LV10AZSI-35L | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 12 Input 10 I/O 35ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| PEEL22LV10AZT-25 | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 12 INP 10 I/O 25ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| PEEL22LV10AZT-25L | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 12 Input 10 I/O 25ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。