- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368009 > PI74FCT162511 (Pericom Semiconductor Corp.) Fast CMOS 16-Bit Registered/Latched Transceiver With Parity PDF資料下載

參數(shù)資料

| 型號(hào): | PI74FCT162511 |

| 廠商: | Pericom Semiconductor Corp. |

| 英文描述: | Fast CMOS 16-Bit Registered/Latched Transceiver With Parity |

| 中文描述: | 快速CMOS 16位注冊(cè)/鎖存校驗(yàn)器 |

| 文件頁(yè)數(shù): | 1/8頁(yè) |

| 文件大小: | 87K |

| 代理商: | PI74FCT162511 |

1

PS2080A 01/15/95

PI74FCT16511/162511T

16-BIT REGISTERED/

PI74FCT162511T

LATCHED TRANSCEIVER WITH PARITY

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

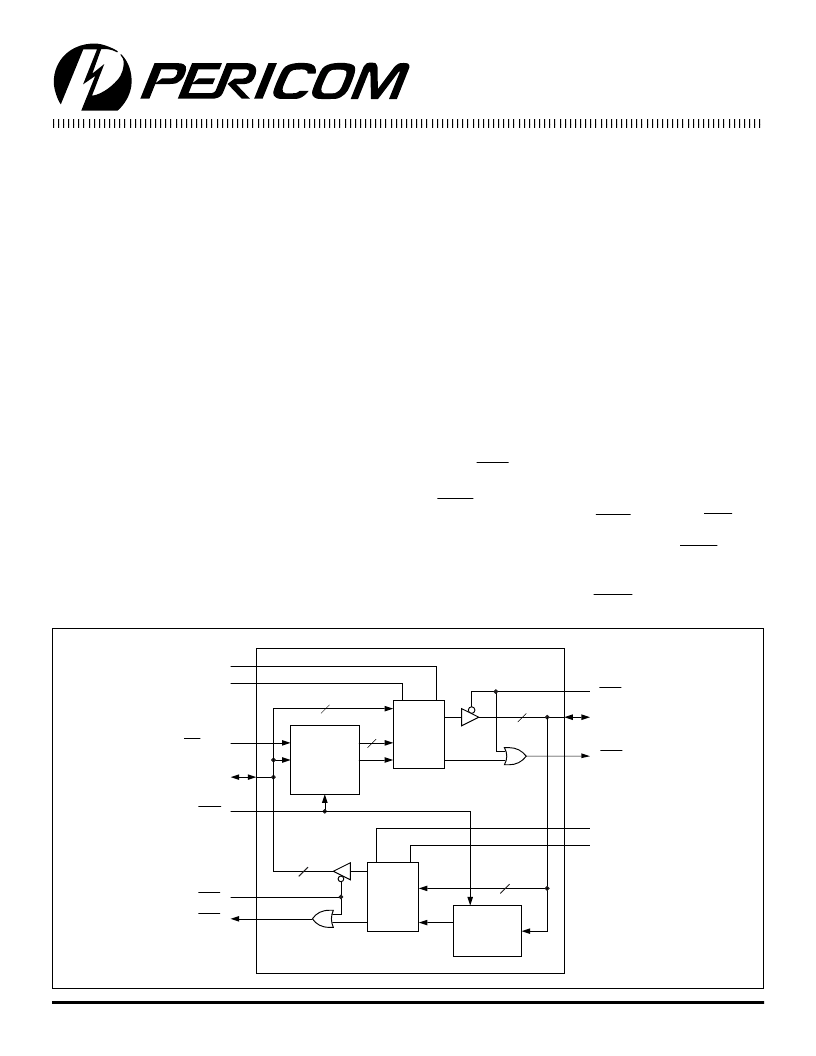

Simplified Logic Block Diagram

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

Fast CMOS 16-Bit Registered/Latched

Transceiver With Parity

Product Features:

Common Features:

PI74FCT16511 and PI74FCT162511 are high-speed, low

power devices with high current drive.

Vcc = 5V ±10%

Typical tsk(o) (Output Skew) < 250 ps, clocked mode

Extended range of –40°C to +85°C

Hysteresis on all inputs

Packages available:

– 56-pin 240 mil wide TSSOP (A)

– 56-pin 300 mil wide SSOP (V)

PI74FCT16511T Features:

High output drive: I

OH

= –32 mA; I

OL

= 64 mA

Power off disable outputs permit “l(fā)ive insertion”

Typical V

OLP

(Output Ground Bounce) < 1.0V

at V

CC

= 5V, T

A

= 25°C

PI74FCT162511T Features:

High output drive: I

OL

/I

OH

= 24 mA

Open drain parity error allows wire-OR

Typical V

OLP

(Output Ground Bounce) < 1.0V

at V

CC

= 5V, T

A

= 25°C

Balanced output drivers: ±24 mA

Series current limiting resistors

Product Description:

Pericom Semiconductor’s PI74FCT series of logic circuits are pro-

duced in the Company’s advanced 0.8 micron CMOS technology,

achieving industry leading speed grades.

The PI74FCT16511T and PI74FCT162511T are high-speed, low-

power 16-bit registered/latched transceiver with parity which

combines D-type latches and D-type flip-flops to allow data flow

in transparent, latched or clocked modes. It has a parity generator/

checker in the A-to-B direction and a parity checker in the B-to-A

direction. Error checking is done at the byte level with separate

parity bits for each byte. One error flag for each direction (A-to-B

or B-to-A) exists to indicate an error for either byte in either

direction. The parity error flags which are open drain outputs, can

be tied together and/or tied with flags from other devices to form a

single error flag or interrupt. To disable the error flag during

combinational transitions, a designer can disable the parity error

flag by the OExx control pins.

The operation in A-to-B direction is controlled by LEAB, CLKAB

and OEAB control pins, and the operation in B-to-A direction is

controlled by LEBA, CLKBA and OEBA control pins. GEN/CHK

is used to select the operation of A-to-B direction, while B-to-A

direction is always in checking mode. The ODD/EVEN select is

common between the two directions. Independent operation can be

achieved between the two directions by using the corresponding

control lines except for the ODD/EVEN control.

Latch/

Register

Byte

Parity

Generator/

Checker

Latch/

Register

Byte

Parity

Checking

2

Parity

16

Data

18

Parity, data

18

Parity, data

18

Parity, data

OEAB

B0-15

PB1,2

PERB

(Open Drain)

LEBA

CLKBA

LEAB

CLKAB

GEN/CHK

A0-15

PA1,2

ODD/EVEN

OEBA

PERA

(Open Drain)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PI74FCT162511T | Fast CMOS 16-Bit Registered/Latched Transceiver With Parity |

| PI74FCT16511T | Fast CMOS 16-Bit Registered/Latched Transceiver With Parity |

| PI74FCT162543T | Fast CMOS 16-Bit Latched Transceivers |

| PI74FCT162H543T | Fast CMOS 16-Bit Latched Transceivers |

| PI74FCT16543T | Fast CMOS 16-Bit Latched Transceivers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PI74FCT162511ATA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Bus Transceiver |

| PI74FCT162511ATV | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Bus Transceiver |

| PI74FCT162511CTA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Bus Transceiver |

| PI74FCT162511CTV | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Bus Transceiver |

| PI74FCT162511T | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:Fast CMOS 16-Bit Registered/Latched Transceiver With Parity |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。