- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368024 > pic16ce625 (Microchip Technology Inc.) OTP 8-Bit CMOS MCU with EEPROM Data Memory(8位OTP CMOS微控制器) PDF資料下載

參數(shù)資料

| 型號: | pic16ce625 |

| 廠商: | Microchip Technology Inc. |

| 英文描述: | OTP 8-Bit CMOS MCU with EEPROM Data Memory(8位OTP CMOS微控制器) |

| 中文描述: | 檢察官辦公室8位CMOS微控制器EEPROM數(shù)據(jù)存儲器(8位檢察官辦公室的CMOS微控制器) |

| 文件頁數(shù): | 65/108頁 |

| 文件大小: | 2355K |

| 代理商: | PIC16CE625 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁當(dāng)前第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁

1998 Microchip Technology Inc.

Preliminary

DS40182A-page 65

PIC16CE62X

11.0

INSTRUCTION SET SUMMARY

Each PIC16CE62X instruction is a 14-bit word divided

into an OPCODE which specifies the instruction type

and one or more operands which further specify the

operation of the instruction. The PIC16CE62X instruc-

tion set summary in Table 11-2 lists

byte-oriented

,

bit-oriented

, and

literal and control

operations.

Table 11-1 shows the opcode field descriptions.

For

byte-oriented

instructions, 'f' represents a file

register designator and 'd' represents a destination

designator. The file register designator specifies which

file register is to be used by the instruction.

The destination designator specifies where the result of

the operation is to be placed. If 'd' is zero, the result is

placed in the W register. If 'd' is one, the result is placed

in the file register specified in the instruction.

For

bit-oriented

instructions, 'b' represents a bit field

designator which selects the number of the bit affected

by the operation, while 'f' represents the number of the

file in which the bit is located.

For

literal and control

operations, 'k' represents an

eight or eleven bit constant or literal value.

TABLE 11-1:

OPCODE FIELD

DESCRIPTIONS

Field

Description

f

W

b

k

x

Register file address (0x00 to 0x7F)

Working register (accumulator)

Bit address within an 8-bit file register

Literal field, constant data or label

Don't care location (= 0 or 1)

The assembler will generate code with x = 0. It is the

recommended form of use for compatibility with all

Microchip software tools.

Destination select; d = 0: store result in W,

d = 1: store result in file register f.

Default is d = 1

label

Label name

TOS

Top of Stack

PC

Program Counter

PCLATH

Program Counter High Latch

GIE

Global Interrupt Enable bit

WDT

Watchdog Timer/Counter

TO

Time-out bit

PD

Power-down bit

dest

Destination either the W register or the specified

register file location

[ ]

Options

( )

Contents

→

Assigned to

< >

Register bit field

∈

In the set of

i

talics User defined term (font is courier)

d

The instruction set is highly orthogonal and is grouped

into three basic categories:

Byte-oriented

operations

Bit-oriented

operations

Literal and control

operations

All instructions are executed within one single

instruction cycle, unless a conditional test is true or the

program counter is changed as a result of an

instruction. In this case, the execution takes two

instruction cycles with the second cycle executed as a

NOP. One instruction cycle consists of four oscillator

periods. Thus, for an oscillator frequency of 4 MHz, the

normal instruction execution time is 1

μ

s. If a

conditional test is true or the program counter is

changed as a result of an instruction, the instruction

execution time is 2

μ

s.

Table 11-1 lists the instructions recognized by the

MPASM assembler.

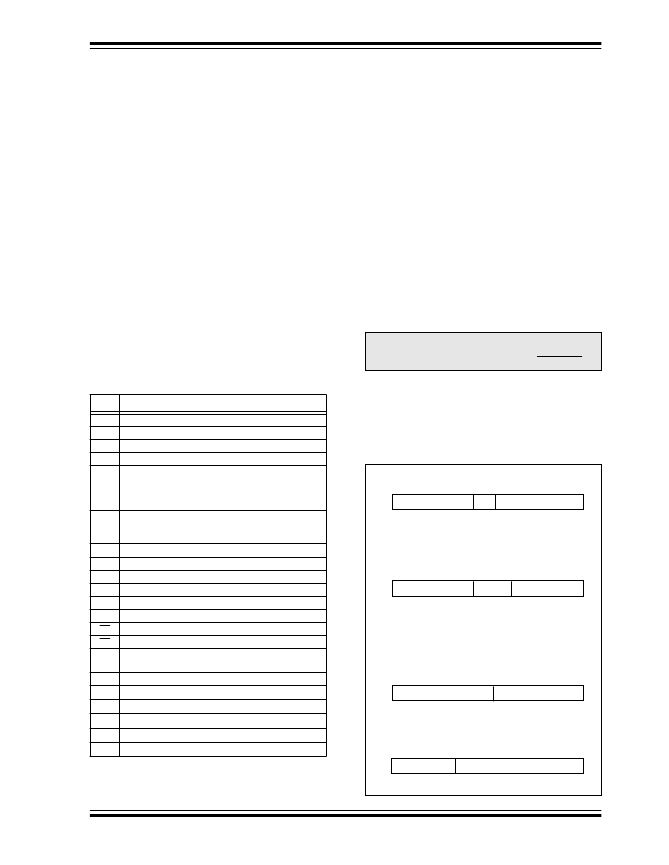

Figure 11-1 shows the three general formats that the

instructions can have.

All examples use the following format to represent a

hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

FIGURE 11-1: GENERAL FORMAT FOR

INSTRUCTIONS

Note:

To maintain upward compatibility with

future PICmicro products, do not use the

OPTION

and

TRIS

instructions.

Byte-oriented

file register operations

13 8 7 6 0

OPCODE d f (FILE #)

d = 0 for destination W

d = 1 for destination f

f = 7-bit file register address

Bit-oriented

file register operations

13 10 9 7 6 0

OPCODE b (BIT #) f (FILE #)

b = 3-bit bit address

f = 7-bit file register address

Literal and control

operations

13 8 7 0

OPCODE k (literal)

k = 8-bit immediate value

13 11 10 0

OPCODE k (literal)

k = 11-bit immediate value

General

CALL

and

GOTO

instructions only

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| pic16cr54c | ROM-Based 8-Bit CMOS Microcontroller Series(8位CMOS微控制器) |

| PIC16CR73 | 28/40-Pin, 8-Bit CMOS ROM Microcontrollers |

| PIC16CR74 | 28/40-Pin, 8-Bit CMOS ROM Microcontrollers |

| PIC16CR76 | 28/40-Pin, 8-Bit CMOS ROM Microcontrollers |

| PIC16CR77 | 28/40-Pin, 8-Bit CMOS ROM Microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PIC16CE625/JW | 功能描述:8位微控制器 -MCU 3.5KB 128 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| PIC16CE625-04/P | 功能描述:8位微控制器 -MCU 3.5KB 128 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| PIC16CE625-04/P | 制造商:Microchip Technology Inc 功能描述:IC 8BIT CMOS MCU 16CE625 DIP18 |

| PIC16CE625-04/SO | 功能描述:8位微控制器 -MCU 3.5KB 128 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| PIC16CE625-04/SS | 功能描述:8位微控制器 -MCU 3.5KB 128 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。