- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368052 > PLUS16L8-7A (NXP SEMICONDUCTORS) PAL devices PDF資料下載

參數(shù)資料

| 型號: | PLUS16L8-7A |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | PLD |

| 英文描述: | PAL devices |

| 中文描述: | OT PLD, 10 ns, PQCC20 |

| 文件頁數(shù): | 13/16頁 |

| 文件大小: | 160K |

| 代理商: | PLUS16L8-7A |

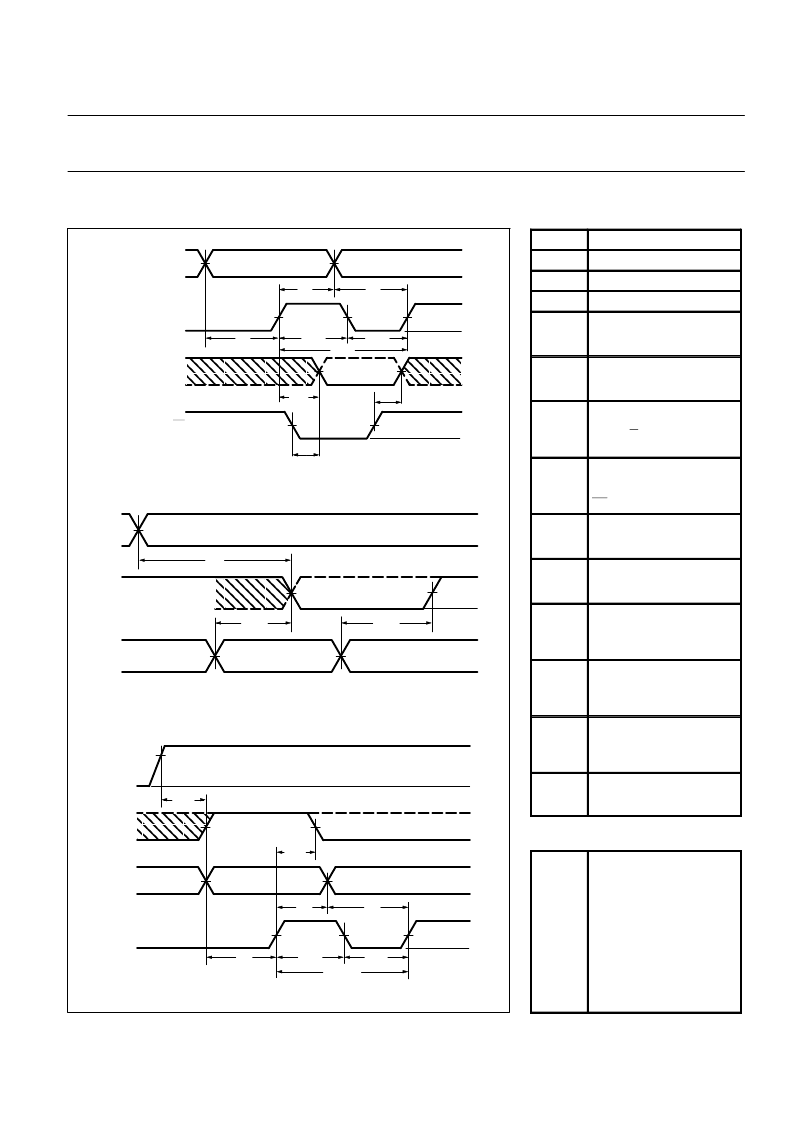

(REGISTERED

OUTPUTS)

PD

OE2

t

CKL

V

t

OD1

t

IS

1.5V

1.5V

1.5V

1.5V

1.5V

1.5V

1.5V

1.5V

+3V

0V

+3V

0V

V

OH

V

OL

+3V

0V

I, B

(INPUTS)

CLK

Q

(REGISTERED OUTPUTS)

OE

t

IH

t

IS

t

CKH

t

CKP

CKO

t

OE1

Flip-Flop Outputs

I, B

(INPUTS)

O, B

(COMBINATORIAL

OUTPUTS)

I, B

(OUTPUT

ENABLE)

t

OD2

1.5V

1.5V

+1.5V

+1.5V

V

T

+3V

0V

V

OH

V

OL

+3V

0V

Gate Outputs

1.5V

1.5V

1.5V

1.5V

1.5V

1.5V

1.5V

0V

V

OH

V

OL

+3V

0V

+3V

0V

V

CC

4.5V

V

CC

Q

I, B

(INPUTS)

CLK

t

CKO

t

IH

t

IS

t

IS

t

CKH

t

CKL

t

IS+

t

CKF

Power–Up Reset

Philips Semiconductors Programmable Logic Devices

Product specification

PLUS16R8D/-7 SERIES

PAL devices

16L8, 16R8, 16R6, 16R4

September 10, 1993

48

TIMING DIAGRAMS

1, 2

NOTES:

1. Input pulse amplitude is 0V to 3V.

2. Input rise and fall times are 2.5ns.

TIMING DEFINITIONS

SYMBOL

PARAMETER

t

CKH

Width of input clock pulse.

t

CKL

Interval between clock pulses.

t

CKP

Clock period.

t

IS

Required delay between

beginning of valid input and

positive transition of clock.

t

IH

Required delay between

positive transition of clock and

end of valid input data.

t

CKF

Delay between positive

transition of clock and when

internal Q output of flip-flop

becomes valid.

t

CKO

Delay between positive

transition of clock and when

outputs become valid (with

OE Low).

t

OE1

Delay between beginning of

Output Enable Low and when

outputs become valid.

t

OD1

Delay between beginning of

Output Enable High and when

outputs are in the Off-State.

t

OE2

Delay between predefined

Output Enable High, and

when combinational outputs

become valid.

t

OD2

Delay between predefined

Output Enable Low and when

combinational outputs are in

the Off-State.

t

PPR

Delay between V

CC

(after

power-on) and when flip-flop

outputs become preset at “1”

(internal Q outputs at “0”).

t

PD

Propagation delay between

combinational inputs and

outputs.

FREQUENCY DEFINITIONS

f

MAX

No feedback:

Determined by

the minimum clock period,

1/(t

CKL

+ t

CKH

).

Internal feedback:

Determined by the internal

delay from flip-flop outputs

through the internal feedback

and array to the flip-flop

inputs, 1/(t

IS

+ t

CKF

).

External feedback:

Determined by clock-to-output

delay and input setup time,

1/(t

IS

+ t

CKO

).

相關PDF資料 |

PDF描述 |

|---|---|

| PLUS16L8-7N | PAL devices |

| PLUS16L8DA | PAL devices |

| PLUS16L8DN | PAL devices |

| PLUS16R4 | PAL devices |

| PLUS16R4-7A | PAL devices |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PLUS16L8-7N | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:PAL devices |

| PLUS16L8DA | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:PAL devices |

| PLUS16L8DN | 制造商:North American Philips Discrete Products Div 功能描述:Simple, Programmable Array Logic, 20 Pin, Plastic, DIP |

| PLUS16R4 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:PAL devices |

| PLUS16R4-7A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:PAL devices |

發(fā)布緊急采購,3分鐘左右您將得到回復。