- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378056 > PM8313 (PMC-Sierra, Inc.) M13 Multiplexer/Demultiplexer PDF資料下載

參數(shù)資料

| 型號: | PM8313 |

| 廠商: | PMC-Sierra, Inc. |

| 英文描述: | M13 Multiplexer/Demultiplexer |

| 中文描述: | M13復(fù)用器/解復(fù)用器 |

| 文件頁數(shù): | 1/2頁 |

| 文件大小: | 59K |

| 代理商: | PM8313 |

PMC-920522 (R10)

1998 PMC-Sierra, Inc. October, 1998

PM8313

D3MX

PMC-Sierra,Inc.

M13 Multiplexer/Demultiplexer

FEATURES

Integrates a complete M13 multiplexer/

demultiplexer in a single monolithic

device.

Integral framer supports the M23 or C-

bit parity DS3 format with path

maintenance datalink processing and

bit-oriented code support for Far-End

Alarm and Control (FEAC) channel

termination.

Supports either the M12 or the G.747

formats to allow DS1 or E1 signals to

be multiplexed into a DS3 signal.

Allows the M12 stages to be bypassed

allowing direct input of DS2 signals.

Generates an interrupt upon detection

of various alarms, events, or changes

in status. Identification of interrupt

sources, masking of interrupt sources,

and acknowledgement of interrupts is

provided via internal registers.

Application-compatible with the

PM4351 COMET T1 Transceiver,

PM4341A T1XC T1 Transceiver,

PM4344 TQUAD Quad T1 Framer,

PM4388 TOCTL Octal T1 Framer,

PM6341 E1XC E1 Transceiver,

PM6344 EQUAD Quad E1 Framer,

PM6388 EOCTL Octal E1 Framer,

PM4314 QDSX Quad E1/T1 LIU, and

the PM7344 S/UNI

-MPH.

Provides a generic 8-bit

microprocessor interface for

configuration, control, and status

monitoring.

Low power 5 V CMOS technology.

Available in a high density (28 by

28 mm) 208-pin Plastic Quad Flat

Pack (PQFP) package.

DS3 FRAMER SECTION

Detects/inserts DS3 Alarm Indication

Signal (AIS) and Idle signal - operates

correctly in the presence of 10-3 Bit

Error Ratio (BER).

Extracts/inserts the X,P,M,F,C and the

stuff opportunity bits and serializes for

optional external processing.

Extracts/inserts the C-bit parity mode

path maintenance datalink and

serializes for optional external

processing.

Extracts/inserts the C-bit parity bit-

oriented codes in the FEAC channel.

Detects and accumulates EXcessive

Zeros (EXZ), Loss Of Signal (LOS),

Line Code Violations (LCVs) P-bit,

F-bit, or M-bit errors, C-bit parity errors

and Far-End Block Errors (FEBEs).

Supports DS3 line loopback and DS3

diagnostic loopback modes to assist in

fault isolation.

M23 AND M12 MULTIPLEX/

DEMULTIPLEX SECTIONS

Supports combination of four DS1 bit

streams or the combination of three E1

bit streams per G.747 into a single

M12 stream.

Supports per-DS2 payload loopback

requests via C-bits or microprocessor

control.

Accumulates DS2 M-bit, F-bit, and

G.747 framing bit/word error events.

Supports DS2 AIS assertion based on

DS3 LOF, or under microprocessor

control.

Supports DS2 tributary AIS activation/

deactivation in either direction under

microprocessor control.

Inserts/detects per-DS1 payload

loopback requests transmitted via

C-bits.

APPLICATIONS

M23 or C-Bit Parity Format DS1 to

DS3 Mux/Demux Equipment

Fractional T3 Access Equipment

DS2-to-DS3 Mux/Demux Equipment

DS1-to-DS3 Mux/Demux Equipment

Supporting G.747 Tributary Format

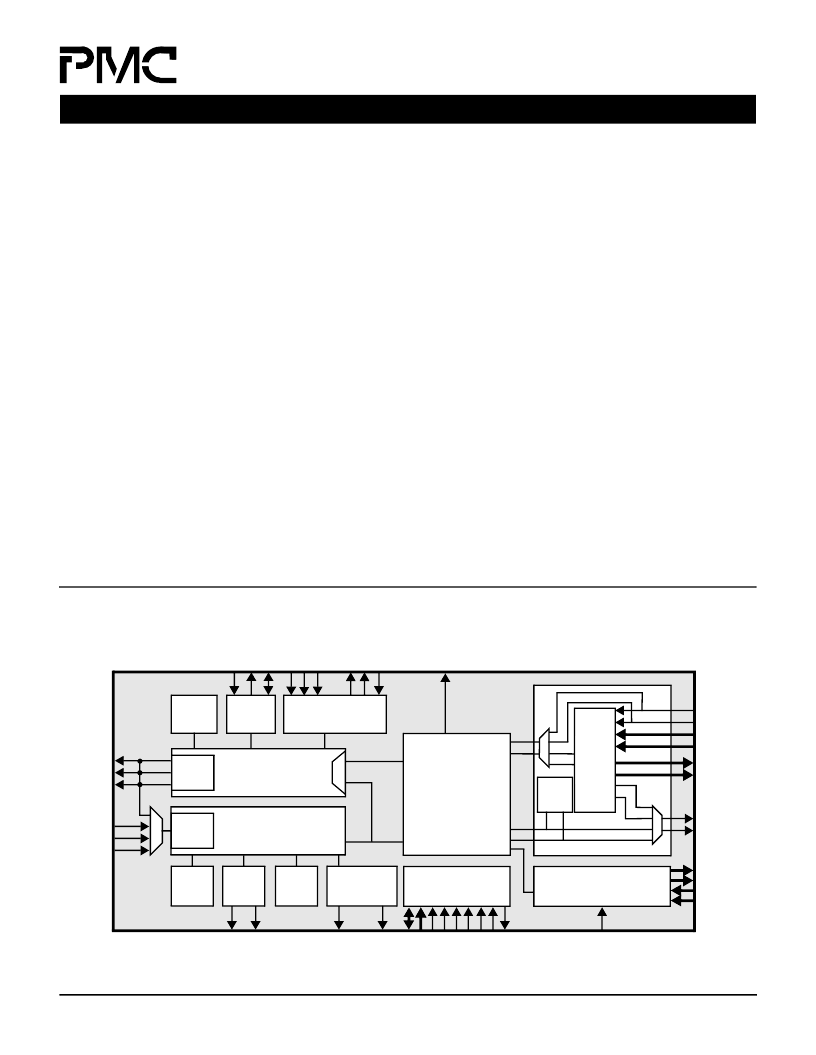

BLOCK DIAGRAM

D

A

A

A

C

W

R

I

TD1CLK[28:5]

TD1DAT[28:5]

RD1CLK[28:5]

RD1DAT[28:5]

One of seven M12

#1

RBOC

Receive

FEAC

DS2

FRMR

XBOC

Transmit

FEAC

RD1CLK4

RD1DAT4

RD1CLK[3:1]

RD1DAT[3:1]

TD1CLK4

TD1DAT4

RD1DAT[3:1]

RD1CLK[3:1]

Remaining Six M12

#2 - #7

PMON

Perfor-

mance

Monitor

Counters

FRMR

DS3 Receive

Framer

B3ZS

Decode

TRAN

DS3 Transmit

Framer

B3ZS

Decode

Tx

O/H

Access

MX23

M23

MUX/DEMUX

RFDL

Receive

HDLC

MPIF

Microprocessor

Interface

R

R

R

R

R

R

R

R

R

R

RCLK/VCLK

RPOS/RDAT

RNEG/RLCV

TCLK

TPOS/TDAT

TNEG/TMFP

T

T

T

T

T

T

T

T

T

XFDL

Transmit

HDLC

G

MX12

M12

MUX/

DEMUX

Rx

O/H

Access

T

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PM8313-RI | M13 MULTIPLEXER |

| PM8315 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| PM8315-PI | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| PM8316 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| PM8316TEMUX-84 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PM8313-RI | 制造商:PMC-Sierra 功能描述: |

| PM8315 | 制造商:PMC 制造商全稱:PMC 功能描述:High Density T1/E1 Framer with Integrated VT/TU Mapper and M13 Mux |

| PM8315-PI | 制造商:PMC-Sierra 功能描述: |

| PM8315-PI-P-RFBD | 制造商:PMC-Sierra 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。