- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368094 > PPC405CR-3BC200C (APPLIEDMICRO INC) PowerPC 405CR Embedded Processor PDF資料下載

參數(shù)資料

| 型號: | PPC405CR-3BC200C |

| 廠商: | APPLIEDMICRO INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | PowerPC 405CR Embedded Processor |

| 中文描述: | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA316 |

| 封裝: | 27 X 27 MM, PLASTIC, EBGA-316 |

| 文件頁數(shù): | 23/42頁 |

| 文件大?。?/td> | 446K |

| 代理商: | PPC405CR-3BC200C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

PPC405CR – PowerPC 405CR Embedded Processor

Revision 1.02 – January 11, 2005

Data Sheet

AMCC

23

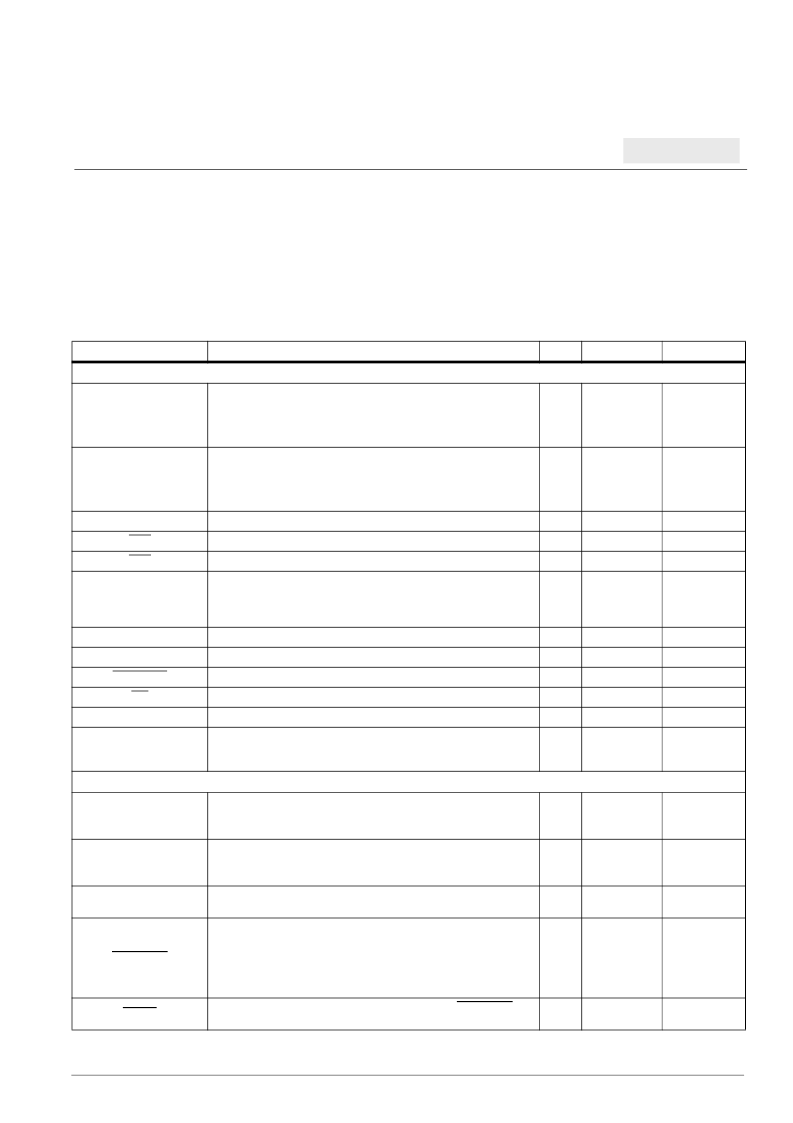

Table 6. Signal Functional Description (Sheet 1 of 5)

Multiplexed signals are shown in brackets following the first signal name assigned to each multiplexed ball.

Notes:

1. Receiver input has hysteresis.

2. Must pull up. See “Pull-Up and Pull-Down Resistors” on page 21 for recommended termination values.

3. Must pull down. See “Pull-Up and Pull-Down Resistors” on page 21 for recommended termination values.

4. If not used, must pull up.

5. If not used, must pull down.

6. Strapping input during reset; pull-up or pull-down required.

7. Pull-up may be required. See “External Bus Control Signals” on page 22.

Signal Name

Description

I/O

Type

Notes

SDRAM Interface

MemData0:31

Memory Data bus.

Notes:

1. MemData0 is the most significant bit (msb).

2. MemData31 is the least significant bit (lsb).

I/O

3.3V LVTTL

MemAddr12:0

Memory Address bus.

Notes:

1. MemAddr12 is the most significant bit (msb).

2. MemAddr0 is the least significant bit (lsb).

O

3.3V LVTTL

BA0:1

Bank Address supporting up to four internal banks.

O

3.3V LVTTL

RAS

Row Address Strobe.

O

3.3V LVTTL

CAS

Column Address Strobe.

O

3.3V LVTTL

DQM0:3

DQM for byte lanes 0 (MemData0:7),

1 (MemData8:15),

2 (MemData16:23), and

3 (MemData24:31).

O

3.3V LVTTL

DQMCB

DQM for ECC check bits.

O

3.3V LVTTL

ECC0:7

ECC check bits 0:7.

I/O

3.3V LVTTL

BankSel0:3

Select up to four external SDRAM banks.

O

3.3V LVTTL

WE

Write Enable.

O

3.3V LVTTL

ClkEn0:1

SDRAM Clock Enable.

O

3.3V LVTTL

MemClkOut0:1

Two copies of an SDRAM clock allows, in some cases, glueless

SDRAM attach without requiring this signal to be repowered by a PLL

or zero-delay buffer.

O

3.3V LVTTL

External Slave Peripheral Interface

PerData0:31

Peripheral data bus used by PPC405CR when not in external master

mode, otherwise used by external master.

Note:

PerData0 is the most significant bit (msb) on this bus.

I/O

5V tolerant

3.3V LVTTL

1

PerAddr0:31

Peripheral address bus used by PPC405CR when not in external

master mode, otherwise used by external master.

Note:

PerAddr0 is the most significant bit (msb) on this bus.

I/O

5V tolerant

3.3V LVTTL

1

PerPar0:3

Peripheral byte parity signals.

I/O

5V tolerant

3.3V LVTTL

1

PerWBE0:3

As outputs, these pins can act as byte-enables which are valid for an

entire cycle or as write-byte-enables which are valid for each byte on

each data transfer, allowing partial word transactions. As outputs,

pins are used by either peripheral controller or the DMA controller

depending upon the type of transfer involved. Used as inputs when

external bus master owns the external interface.

I/O

5V tolerant

3.3V LVTTL

1, 7

PerWE

Peripheral write enable. Active when any of the four PerWBE0:3

signals are active.

O

5V tolerant

3.3V LVTTL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PPC405CR-3BC200CZ | PowerPC 405CR Embedded Processor |

| PPC405CR-3BC266C | PowerPC 405CR Embedded Processor |

| PPC405CR-3BC266CZ | PowerPC 405CR Embedded Processor |

| PPC405CR-3KC133C | PowerPC 405CR Embedded Processor |

| PPC405CR-3KC133CZ | PowerPC 405CR Embedded Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PPC405CR-3BC200CZ | 制造商:AppliedMicro 功能描述:MPU 405CR RISC 32BIT 0.25UM 200MHZ 3.3V 316PIN EBGA - Tape and Reel |

| PPC405CR-3BC266C | 制造商:AMCC 制造商全稱:Applied Micro Circuits Corporation 功能描述:PowerPC 405CR Embedded Processor |

| PPC405CR-3BC266CZ | 制造商:AppliedMicro 功能描述:MPU 405CR RISC 32BIT 0.25UM 266MHZ 3.3V 316PIN EBGA - Tape and Reel |

| PPC405CR-3KC133C | 制造商:AppliedMicro 功能描述:MPU 405CR RISC 32-Bit 0.25um 133MHz 3.3V 316-Pin EBGA Tray |

| PPC405CR-3KC133CZ | 制造商:AppliedMicro 功能描述:MPU 405CR RISC 32-Bit 0.25um 133MHz 3.3V 316-Pin EBGA T/R 制造商:AppliedMicro 功能描述:MPU 405CR RISC 32BIT 0.25UM 133MHZ 3.3V 316PIN EBGA - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。