- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368111 > PR31100 (NXP Semiconductors N.V.) Highly integrated embedded processor PDF資料下載

參數(shù)資料

| 型號(hào): | PR31100 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Highly integrated embedded processor |

| 中文描述: | 高度集成的嵌入式處理器 |

| 文件頁(yè)數(shù): | 11/26頁(yè) |

| 文件大小: | 282K |

| 代理商: | PR31100 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)

Philips Semiconductors

Preliminary specification

MIPS

PR31100

Highly integrated embedded processor

1996 Aug 07

11

PIN #

NAME AND FUNCTION

TYPE

NAME

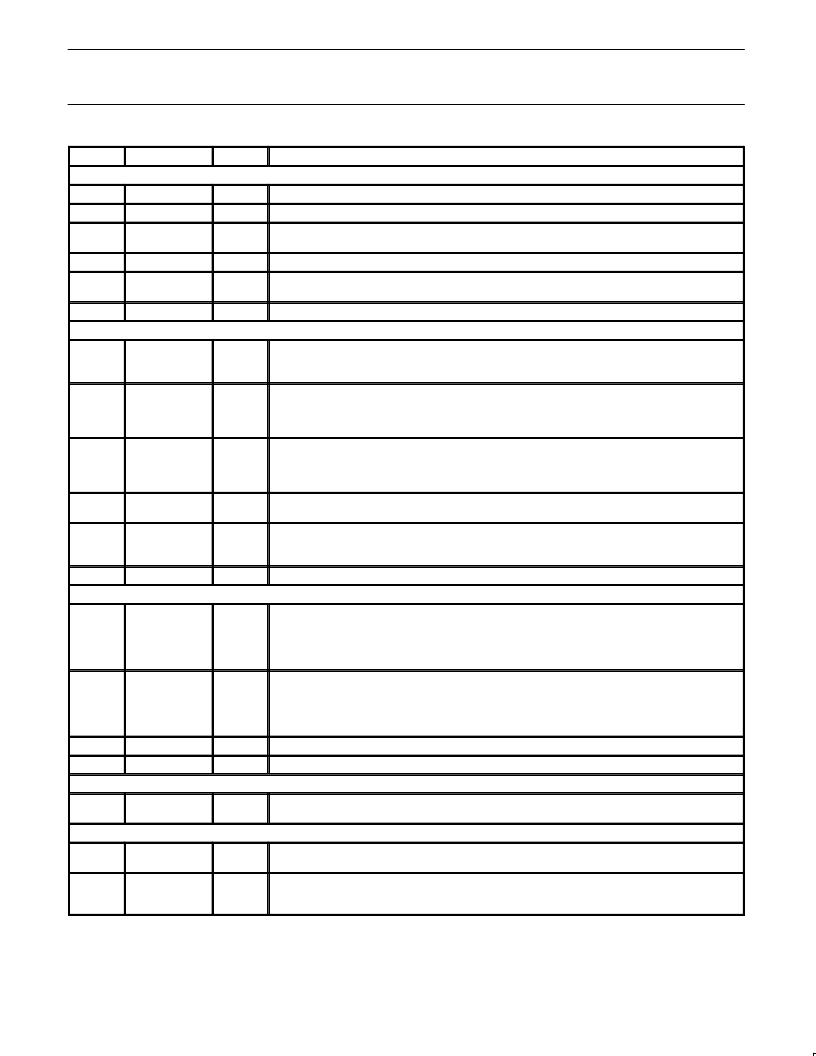

UART and IR Pins

55

TXD

O

This pin is the UART transmit signal from the UARTA module.

54

RXD

I

This pin is the UART receive signal to the UARTA module.

59

IROUT

O

This pin is the UART transmit signal from the UARTB module or the Consumer IR output signal if

Consumer IR mode is enabled.

58

IRIN

I

This pin is the UART receive signal to the UARTB module.

RXPWR

O

This pin is the receiver power output control signal to the external communication IR analog

circuitry.

62

CARDET

I

This pin is the carrier detect input signal from the external communication IR analog circuitry.

Video Pins

91

FRAME

O

This pin is the frame synchronization pulse signal between the Video Module and the LCD, and is

used by the LCD to return it’s pointers to the top of the display. The Video Module asserts FRAME

after all the lines of the LCD have been shifted and transferred, producing a full frame of display.

93

DF

O

This pin is the AC signal for the LCD. Since LCD plasma tends to deteriorate whenever subjected

to a DC voltage, the DF signal is used by the LCD to alternate the polarity of the row and column

voltages used to turn the pixels on and off. The DF signal can be configured to toggle on every

frame or can be configured to toggle every programmable number of LOAD signals.

94

LOAD

O

This pin is the line synchronization pulse signal between the Video Module and the LCD, and is

used by the LCD to transfer the contents of it’s horizontal line shift register to the LCD panel for

display. The Video Module asserts LOAD after an entire horizontal line of data has been shifted

into the LCD.

95

CP

O

This pin is the clock signal for the LCD. Data is pushed by the Video Module on the rising edge of

CP and sampled by the LCD on the falling edge of CP.

101, 100,

99, 98

VDAT(3:0)

O

These pins are the data for the LCD. These signals are directly connected to the LCD for 4–bit

non–split displays. For 4–bit split and 8–bit non–split displays, an external register is required to

demultiplex the 4–bit data into the desired 8 parallel data lines needed for the LCD.

90

DISPON

O

This pin is the display–on enable signal for the LCD.

Test Pins

74

TESTSIU

I

This pin allows external logic to initiate read or write transactions to PR31100 registers. The

TESTSIU mode is enabled by toggling this signal after the device has powered up. Once the

function is enabled, if the TESTSIU pin is high when the bus is arbitrated (using /DREQ and

/DGRNT), then external logic can initiate read and write transactions to PR31100 registers. This

pin is used for debugging purposes only.

71

TESTCPU

I

This pin allows numerous internal CPU core signals to be brought to external PR31100 pins, in

place of the normal signals assigned to these pins. The CPU core signals assigned to their

respective pins during TESTCPU mode are vendor–dependent. The TESTCPU mode is enabled

by asserting this TESTCPU signal, and this function is provided for generating test vectors for the

CPU core. This pin is used for debugging purposes only.

72

TESTIN

I

This pin is reserved for vendor–dependent use. This pin is used for debugging purposes only.

73

TESTOUT

O

This pin is reserved for vendor–dependent use. This pin is used for debugging purposes only.

Spare Pins

NC4–1

No

Connect

These pins are reserved for future use and should be left unconnected.

Power Supply Pins

VDD (34 each)

+3.3V

These pins are the power pins for PR31100 and should be connected to the digital +3.3V power

supply VSTANDBY.

VSS (34 each)

GND

These pins are the ground pins for PR31100 and should be connected to digital ground. NOTE:

For some vendor–dependent implementations of PR31100, pin 131 may be used for a filter

capacitor for the SYSCLK oscillator (capacitor connected between pin 131 and digital ground).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PR31500ABC | Poseidon embedded processor |

| PR31500 | Poseidon Embedded Processor(Poseidon 嵌入式處理器) |

| PR31700 | 32-bit RISC Microprocessor(32位 RISC微處理器) |

| PR31MA11NTZ | Solid State Relay |

| PR3200 | DIFFERENTIAL PRESSURE TRANSMITTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PR31100ABC | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Highly integrated embedded processor |

| PR31154 S L8EH | 制造商:Intel 功能描述:BRIDGE 31154 SL8EH PBGA421 |

| PR312/6DC | 制造商:Panasonic 功能描述:Pack |

| PR31500 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Poseidon embedded processor |

| PR31500ABC | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Poseidon embedded processor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。