- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368148 > PSD401A1-20J Field-Programmable Peripheral PDF資料下載

參數(shù)資料

| 型號(hào): | PSD401A1-20J |

| 英文描述: | Field-Programmable Peripheral |

| 中文描述: | 現(xiàn)場(chǎng)可編程外圍 |

| 文件頁(yè)數(shù): | 11/123頁(yè) |

| 文件大小: | 657K |

| 代理商: | PSD401A1-20J |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)

PSD4XX Famly

8

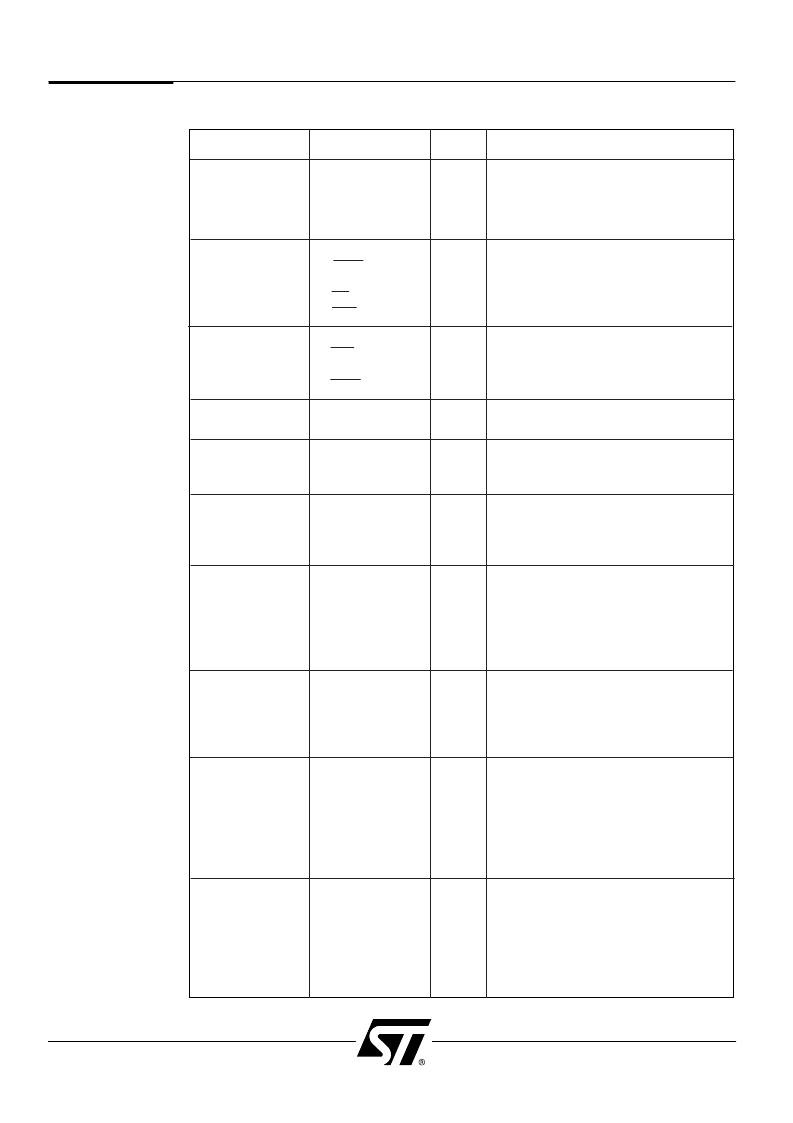

Pin Name

Pin Function

Type

Function Descriptions

ADIO0 – ADIO15

Address/data bus

I/O

1. Address/data bus, multiplexed

bus mode

2. Address bus, non-multiplexed

bus mode

RD

Multiple Names

1. Read

2. E

3. DS

4. LDS

I

Multiple functions

1. Read signal

2. E signal (Clock)

3. Data strobe signal

4. Low byte data strobe

WR

Multiple Names

1. WR

2. R/W

3. WRL

I

Multiple functions

1. Write signal

2. Read-write signal

3. Low byte write signal

CSI

Chip Select Input

I

Active low, select PSD4XX

standby mode if high.

RESET

Reset Input

I

Reset I/O ports, ZPLD/macrocells,

and Configuration Registers.

Active low.

CLKIN

Input clock

I

Clock input to ZPLD macrocells,

ZPLD Array and APD counter.

Connect to ground if Clock Input

not used.

PA0 – PA7

I/O Port A

I/O

Multiple functions

1. I/O port

2. ZPLD/macrocell I/O port

3. Latched address outputs

(PA0 – PA7)

→

(A0 – A7)

4. High address inputs (A16 – A23)

PB0 – PB7

I/O Port B

I/O

Multiple functions

1. I/O port

2. ZPLD/macrocell I/O port

3. Latched address outputs

(PB0–PB7)

→

(A0–A7) or (A8–A15)

PC0 – PC7

I/O Port C

I/O

Multiple functions

1. I/O port

2. ZPLD input port

*

3. Latched address outputs

(PC0 – PC7)

→

(A0–A7)

4. Data Port (D0 – D7,

non-multiplexed bus)

CMOS

or

OD

PD0 – PD7

I/O Port D

I/O

Multiple functions

1. I/O port

2. ZPLD input port

*

3. Latched address outputs

(PD0–PD7)

→

(A0–A7) or (A8–A15)

4. Data Port (D8–D15,

non-multiplexed bus)

CMOS

or

OD

8.0

Table 2.

PSD4XX Pin

Descriptions

The following table describes the pin names and pin functions of the PSD4XX. Pins that

have multiple names and/or functions are defined by user configuration.

*

Available only in PSD4XXA2 and ZPSD4XXA2 Series.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PSD401A1-20JI | Field-Programmable Peripheral |

| PSD401A1-20LI | Field-Programmable Peripheral |

| PSD401A1-20LM | Field-Programmable Peripheral |

| PSD401A1-20U | Field-Programmable Peripheral |

| PSD401A1-20UI | Field-Programmable Peripheral |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PSD401A1-20JI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Peripheral |

| PSD401A1-20LI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Peripheral |

| PSD401A1-20LM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Peripheral |

| PSD401A1-20U | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Peripheral |

| PSD401A1-20UI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Peripheral |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。