- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376264 > PSD854212MT (意法半導(dǎo)體) Flash In-System Programmable ISP Peripherals For 8-bit MCUs PDF資料下載

參數(shù)資料

| 型號(hào): | PSD854212MT |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| 中文描述: | Flash在系統(tǒng)可編程ISP的外設(shè)的8位微控制器 |

| 文件頁數(shù): | 89/110頁 |

| 文件大小: | 1737K |

| 代理商: | PSD854212MT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁當(dāng)前第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁

89/110

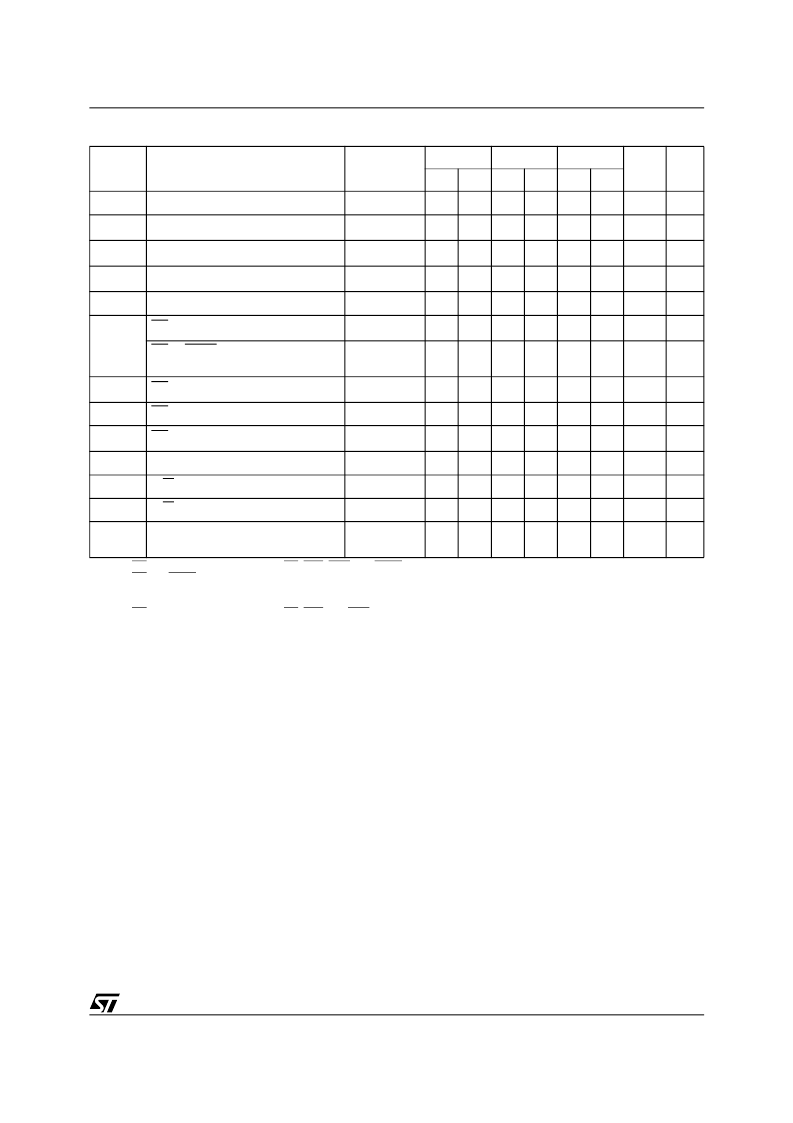

PSD813F2, PSD833F2, PSD834F2, PSD853F2, PSD854F2

Table 56. READ Timing (3V devices)

Note: 1. RD timing has the same timing as DS, LDS, UDS, and PSEN signals.

2. RD and PSEN have the same timing for 8031.

3. Any input used to select an internal PSD function.

4. In multiplexed mode latched address generated from ADIO delay to address output on any Port.

5. RD timing has the same timing as DS, LDS, and UDS signals.

Symbol

Parameter

Conditions

-12

-15

-20

Turbo

Off

Unit

Min

Max

Min

Max

Min

Max

t

LVLX

ALE or AS Pulse Width

26

26

30

ns

t

AVLX

Address Setup Time

(Note

3

)

9

10

12

ns

t

LXAX

Address Hold Time

(Note

3

)

9

12

14

ns

t

AVQV

Address Valid to Data Valid

(Note

3

)

120

150

200

+ 20

ns

t

SLQV

CS Valid to Data Valid

120

150

200

ns

t

RLQV

RD to Data Valid 8-Bit Bus

(Note

5

)

35

35

40

ns

RD or PSEN to Data Valid 8-Bit Bus,

8031, 80251

(Note

2

)

45

50

55

ns

t

RHQX

RD Data Hold Time

(Note

1

)

0

0

0

ns

t

RLRH

RD Pulse Width

38

40

45

ns

t

RHQZ

RD to Data High-Z

(Note

1

)

38

40

45

ns

t

EHEL

E Pulse Width

40

45

52

ns

t

THEH

R/W Setup Time to Enable

15

18

20

ns

t

ELTL

R/W Hold Time After Enable

0

0

0

ns

t

AVPV

Address Input Valid to

Address Output Delay

(Note

4

)

33

35

40

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PSD854215JT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD854215MT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD854270JIT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD854F3V-90 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD9132V15MT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PSD854F2-15J | 制造商:STMicroelectronics 功能描述:4556DIE2HR - Trays |

| PSD854F2-70J | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 2M 70ns RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD854F2-70M | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 2M 70ns RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD854F2-90J | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 2M 90ns RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD854F2-90JI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 2M 90ns RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。