- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368270 > PSD935F1V-C-12JI (意法半導體) Configurable Memory System on a Chip for 8-Bit Microcontrollers PDF資料下載

參數(shù)資料

| 型號: | PSD935F1V-C-12JI |

| 廠商: | 意法半導體 |

| 英文描述: | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| 中文描述: | 在8片位微控制器可配置存儲系統(tǒng) |

| 文件頁數(shù): | 14/91頁 |

| 文件大?。?/td> | 488K |

| 代理商: | PSD935F1V-C-12JI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁

PSD935G2

PSD9XX Family

13

8.0

Register Bit

Definition

(cont.)

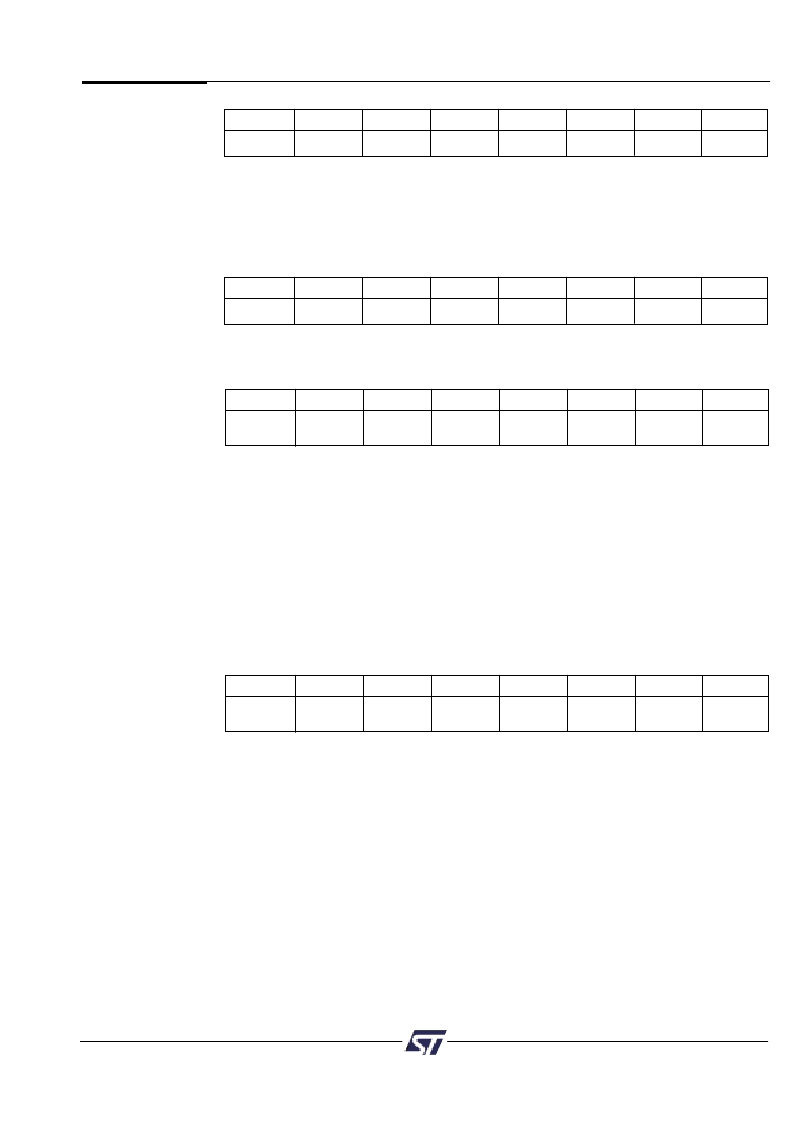

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Security_Bit

*

*

*

Sec3_Prot

Sec2_Prot

Sec1_Prot Sec0_Prot

Flash Boot Protection Register

Bit definitions:

Sec<i>_Prot

Sec<i>_Prot

1 = Boot Block Sector <i> is write protected.

0 = Boot Block Sector <i> is not write protected.

Security_Bit

0 = Security Bit in device has not been set.

1 = Security Bit in device has been set.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Pgr7

Pgr6

Pgr5

Pgr4

Pgr3

Pgr2

Pgr1

Pgr0

Page Register

Bit definitions:

Configure Page input to PLD. Default Pgr[7:0] = 00.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

*

*

PLD

PLD

array-clk

PLD

Turbo

*

APD

enable

*

Mcells clk

PMMR0 Register

Bit definitions: (default is 0)

Bit 1 0 = Automatic Power Down (APD) is disabled.

1 = Automatic Power Down (APD) is enabled.

Bit 3 0 = PLD Turbo is on.

1 = PLD Turbo is off, saving power.

Bit 4 0 = CLKIN input to the PLD AND array is connected.

Every CLKIN change will power up the PLD when Turbo bit is off.

1 = CLKIN input to PLD AND array is disconnected, saving power.

Bit 5 0 = CLKIN input to the PLD Micro

Cells is connected.

1 = CLKIN input to the PLD Micro

Cells is disconnected, saving power.

*

Not used bit should be set to zero.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

*

PLD

PLD

PLD

PLD

PLD

*

PLD

array DBE

array Ale

array Cntl2 array Cntl1 array Cntl0

array addr

PMMR2 Register

Bit definitions (defauld is 0):

Bit 0 0 = Address A[7:0] are connected into the PLD array.

1 = Address A[7:0] are blocked from the PLD array, saving power.

Note: in XA mode, A3-0 come from PF3-0 and A7-4 come from ADIO7-4.

Bit 2 0 = Cntl0 input to the PLD AND array is connected.

1 = Cntl0 input to the PLD AND array is disconnected, saving power.

Bit 3 0 = Cntl1 input to the PLD AND array is connected.

1 = Cntl1 input to the PLD AND array is disconnected, saving power.

Bit 4 0 = Cntl2 input to the PLD AND array is connected.

1 = Cntl2 input to the PLD AND array is disconnected, saving power.

Bit 5 0 = Ale input to the PLD AND array is connected.

1 = Ale input to the PLD AND array is disconnected, saving power.

Bit 6 0 = DBE input to the PLD AND array is connected.

1 = DBE input to the PLD AND array is disconnected, saving power.

*

Not used bit should be set to zero.

相關PDF資料 |

PDF描述 |

|---|---|

| PSD935F1V-C-12M | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD935F1V-C-12MI | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD935F1V-C-12U | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD935F1V-C-12UI | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD935F1V-C-15B81 | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PSD935G2-90U | 功能描述:SPLD - 簡單可編程邏輯器件 TQFP-80 5V 4M 90N RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池數(shù)量:10 最大工作頻率:66 MHz 延遲時間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風格:Through Hole 封裝 / 箱體:DIP-24 |

| PSD935G2V-90U | 功能描述:SPLD - 簡單可編程邏輯器件 U 511-PSD835G2V-90U RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池數(shù)量:10 最大工作頻率:66 MHz 延遲時間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風格:Through Hole 封裝 / 箱體:DIP-24 |

| PSD954F2-90J | 功能描述:SPLD - 簡單可編程邏輯器件 U 511-PSD854F2-90J RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池數(shù)量:10 最大工作頻率:66 MHz 延遲時間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風格:Through Hole 封裝 / 箱體:DIP-24 |

| PSD954F2-90M | 功能描述:SPLD - 簡單可編程邏輯器件 U 511-PSD854F2-90M RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池數(shù)量:10 最大工作頻率:66 MHz 延遲時間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風格:Through Hole 封裝 / 箱體:DIP-24 |

| PSD954F2V-90J | 功能描述:SPLD - 簡單可編程邏輯器件 5.0V 2M 90ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池數(shù)量:10 最大工作頻率:66 MHz 延遲時間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風格:Through Hole 封裝 / 箱體:DIP-24 |

發(fā)布緊急采購,3分鐘左右您將得到回復。