- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376273 > PSD9533V20MT (意法半導(dǎo)體) Flash In-System Programmable ISP Peripherals For 8-bit MCUs PDF資料下載

參數(shù)資料

| 型號(hào): | PSD9533V20MT |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| 中文描述: | Flash在系統(tǒng)可編程ISP的外設(shè)的8位微控制器 |

| 文件頁數(shù): | 64/110頁 |

| 文件大?。?/td> | 1737K |

| 代理商: | PSD9533V20MT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁當(dāng)前第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁

PSD813F2, PSD833F2, PSD834F2, PSD853F2, PSD854F2

64/110

For Users of the HC11 (or compatible)

The HC11 turns off its E clock when it sleeps.

Therefore, if you are using an HC11 (or compati-

ble) in your design, and you wish to use the Pow-

er-down mode, you must not connect the E clock

to CLKIN (PD1). You should instead connect a

crystal oscillator to CLKIN (PD1). The crystal oscil-

lator frequency must be

less than

15 times the fre-

quency of AS. The reason for this is that if the

frequency is greater than 15 times the frequency

of AS, the PSD keeps going into Power-down

mode.

Other Power Saving Options

The PSD offers other reduced power saving op-

tions that are independent of the Power-down

mode. Except for the SRAM Stand-by and PSD

Chip Select Input (CSI, PD2) features, they are en-

abled by setting bits in PMMR0 and PMMR2.

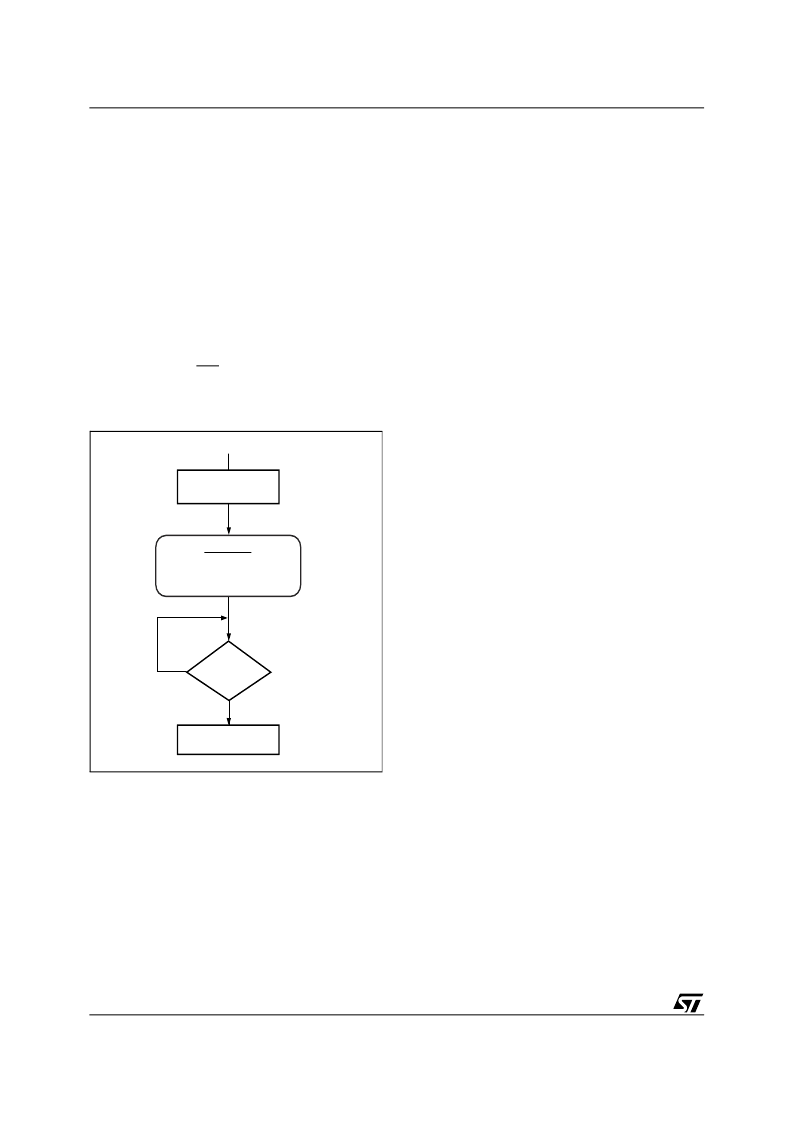

Figure 33. Enable Power-down Flow Chart

PLD Power Management

The power and speed of the PLDs are controlled

by the Turbo Bit (Bit 3) in PMMR0. By setting the

bit to '1,' the Turbo mode is off and the PLDs con-

sume the specified stand-by current when the in-

puts are not switching for an extended time of

70ns. The propagation delay time is increased by

10ns after the Turbo Bit is set to '1' (turned off)

when the inputs change at a composite frequency

of less than 15 MHz. When the Turbo Bit is reset

to '0' (turned on), the PLDs run at full power and

speed. The Turbo Bit affects the PLD’s DC power,

AC power, and propagation delay.

Blocking MCU control signals with the bits of

PMMR2 can further reduce PLD AC power con-

sumption.

SRAM Standby Mode (Battery Backup).

The

PSD supports a battery backup mode in which the

contents of the SRAM are retained in the event of

a power loss. The SRAM has Voltage Stand-by

(V

STBY

, PC2) that can be connected to an external

battery. When V

CC

becomes lower than V

STBY

then the PSD automatically connects to Voltage

Stand-by (V

STBY

, PC2) as a power source to the

SRAM. The SRAM Standby Current (I

STBY

) is typ-

ically 0.5μA. The SRAM data retention voltage is

2V minimum. The Battery-on Indicator (VBATON)

can be routed to PC4. This signal indicates when

the V

CC

has dropped below V

STBY

.

Enable APD

Set PMMR0 Bit 1 = 1

PSD in Power

Down Mode

ALE/AS idle

for 15 CLKIN

clocks

RESET

Yes

No

OPTIONAL

Disable desired inputs to PLD

by setting PMMR0 bits 4 and 5

and PMMR2 bits 2 through 6.

AI02892

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PSD9533V70MT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD9533V90MIT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD9533V90MT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD953412JIT | BiCMOS Power Factor Preregulator 16-PDIP -40 to 85 |

| PSD953412JT | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PSD954F2-90J | 功能描述:SPLD - 簡單可編程邏輯器件 U 511-PSD854F2-90J RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| PSD954F2-90M | 功能描述:SPLD - 簡單可編程邏輯器件 U 511-PSD854F2-90M RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| PSD954F2V-90J | 功能描述:SPLD - 簡單可編程邏輯器件 5.0V 2M 90ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| PSD954F2V-90M | 功能描述:SPLD - 簡單可編程邏輯器件 PQFP-52 3V 2M 90NS RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| PS-DA0104-01 | 制造商:POWER-SYSTEMS 制造商全稱:Power Systems GmbH+Co.KG 功能描述:DC-AC INVERTER UNIT 4 W SINGLE OUTPUTS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。