- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368396 > PZ3128-S10A84 IC-SM-CMOS PLD PDF資料下載

參數(shù)資料

| 型號: | PZ3128-S10A84 |

| 英文描述: | IC-SM-CMOS PLD |

| 中文描述: | 集成電路釤的CMOS可編程邏輯器件 |

| 文件頁數(shù): | 7/18頁 |

| 文件大?。?/td> | 161K |

| 代理商: | PZ3128-S10A84 |

R

XCR3128: 128 Macrocell CPLD

7

www.xilinx.com

1-800-255-7778

DS034 (v1.3) October 9, 2000

This product has been discontinued. Please see

for details.XCR3128, the TAP Port includes four of the five pins (refer

to

Table 2

) described in the JTAG specification: TCK, TMS,

TDI, and TDO. The fifth signal defined by the JTAG specifi-

cation is TRST* (Test Reset). TRST* is considered an

optional signal, since it is not actually required to perform

BST or ISP. The Xilinx XCR3128 saves an I/O pin for gen-

eral purpose use by not implementing the optional TRST*

signal in the JTAG interface. Instead, the Xilinx XCR3128

supports the test reset functionality through the use of its

power up reset circuit, which is included in all Xilinx CPLDs.

The pins associated with the power up reset circuit should

connect to an external pull-up resistor to keep the JTAG

signals from floating when they are not being used.

In the Xilinx XCR3128, the four mandatory JTAG pins each

require a unique, dedicated pin on the device. However, if

JTAG and ISP are not desired in the end-application, these

pins may instead be used as additional general I/O pins.

The decision as to whether these pins are used for

JTAG/ISP or as general I/O is made when the JEDEC file is

generated. If the use of JTAG/ISP is selected, the dedi-

cated pins are not available for general purpose use. How-

ever, unlike competing CPLD

’

s, the Xilinx XCR3128 does

allow the macrocell logic associated with these dedicated

pins to be used as buried logic even when JTAG/ISP is

selected.

Table 3

defines the dedicated pins used by the

four mandatory JTAG signals for each of the XCR3128

package types.

The JTAG specifications defines two sets of commands to

support boundary-scan testing: high-level commands and

low-level commands. High-level commands are executed

via board test software on an a user test station such as

automated test equipment, a PC, or an engineering work-

station (EWS). Each high-level command comprises a

sequence of low level commands. These low-level com-

mands are executed within the component under test, and

therefore must be implemented as part of the TAP Control-

ler design. The set of low-level boundary-scan commands

implemented in the Xilinx XCR3128 is defined in

Table 4

.

By supporting this set of low-level commands, the

XCR3128 allows execution of all high-level boundary-scan

commands.

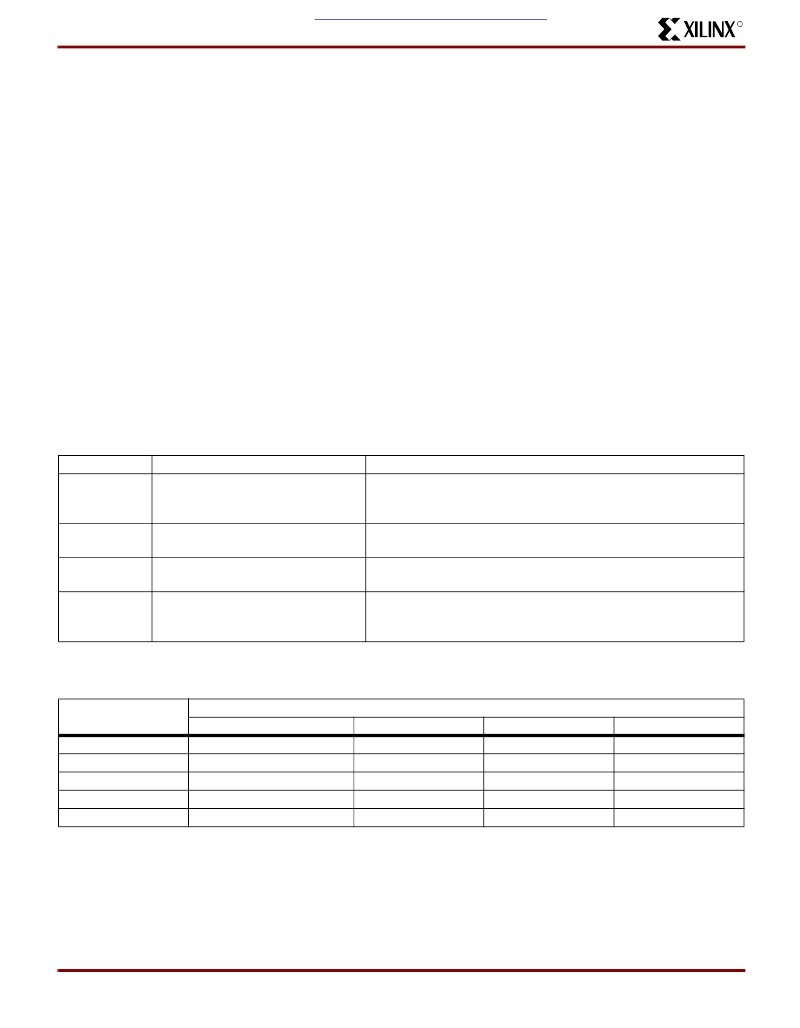

Table 2: JTAG Pin Description

PIN

TCK

NAME

DESCRIPTION

Test Clock Output

Clock pin to shift the serial data and instructions in and out of the

TDI and TDO pins, respectively. TCK is also used to clock the TAP

Controller state machine.

Serial input pin selects the JTAG instruction mode. TMS should be

driven high during user mode operation.

Serial input pin for instructions and test data. Data is shifted in on

the rising edge of TCK.

Serial output pin for instructions and test data. Data is shifted out on

the falling edge of TCK. The signal is tri-stated if data is not being

shifted out of the device.

TMS

Test Mode Select

TDI

Test Data Input

TDO

Test Data Output

Table 3: XCR3128 JTAG Pinout by Package Type

Device

XCR3128

84-pin PLCC

100-pin PQFP

100-pin VQFP

128-pin TQFP

160-pin PQFP

(Pin Number / Macrocell #)

TMS

23 / 48 (C15)

17 / 48 (C15)

15 / 48 (C15)

21 / 48 (C15)

22 / 48 (C15)

TCK

TDI

TDO

62 / 96 (F15)

64 / 96 (F15)

62 / 96 (F15)

82 / 96 (F15)

99 / 96 (F15)

14 / 32 (B15)

6 / 32 (B15)

4 / 32 (B15)

8 / 32 (B15)

9 / 32 (B15)

71 / 112 (G15)

75 / 112 (G15)

73 / 112 (G15)

95 / 112 (G15)

112/ 112 (G15)

相關PDF資料 |

PDF描述 |

|---|---|

| PZ3128-S10BB1 | Electrically-Erasable Complex PLD |

| PZ3128-S10BB1-S | Electrically-Erasable Complex PLD |

| PZ3128-S10BB2 | Electrically-Erasable Complex PLD |

| PZ3128-S10BE | Electrically-Erasable Complex PLD |

| PZ3128-S10BE-S | Electrically-Erasable Complex PLD |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PZ32146-0120 | 制造商:Foxconn 功能描述: |

| PZ37047-S01-A | 制造商:Foxconn 功能描述:Pga Socket, 370 Contacts, 19x19i, 0.05 Row Spacing, Pc Tail Terminal |

| PZ37047-S01-S | 制造商:Foxconn 功能描述:Pga Socket, 370 Contacts, 19x19i, 0.050 Row Spacing, Pc Tail Terminal |

| PZ3X1-15/16 | 制造商:Eclipse Tools 功能描述: |

| PZ-4-3 | 制造商:RICHARD MANNO 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。