- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361242 > Q67127-C1032 (SIEMENS AG) 8-Bit CMOS Microcontroller PDF資料下載

參數(shù)資料

| 型號: | Q67127-C1032 |

| 廠商: | SIEMENS AG |

| 元件分類: | 8位微控制器 |

| 英文描述: | 8-Bit CMOS Microcontroller |

| 中文描述: | 8位CMOS微控制器 |

| 文件頁數(shù): | 4/48頁 |

| 文件大小: | 319K |

| 代理商: | Q67127-C1032 |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

C501

Semiconductor Group

4

1997-04-01

The C501-1R contains a non-volatile 8K

write data memory, four ports, three 16-bit timers counters, a seven source, two priority level

interrupt structure and a serial port. The C501-L is identical, except that it lacks the program

memory on chip. The C501-1E contains a one-time programmable (OTP) program memory on chip.

The term C501 refers to all versions within this specification unless otherwise noted. Further, the

term C501 refers to all versions which are available in the different temperature ranges, marked with

SAB-C501... or SAF-C501....

.

×

8 read-only program memory, a volatile 256

×

8 read/

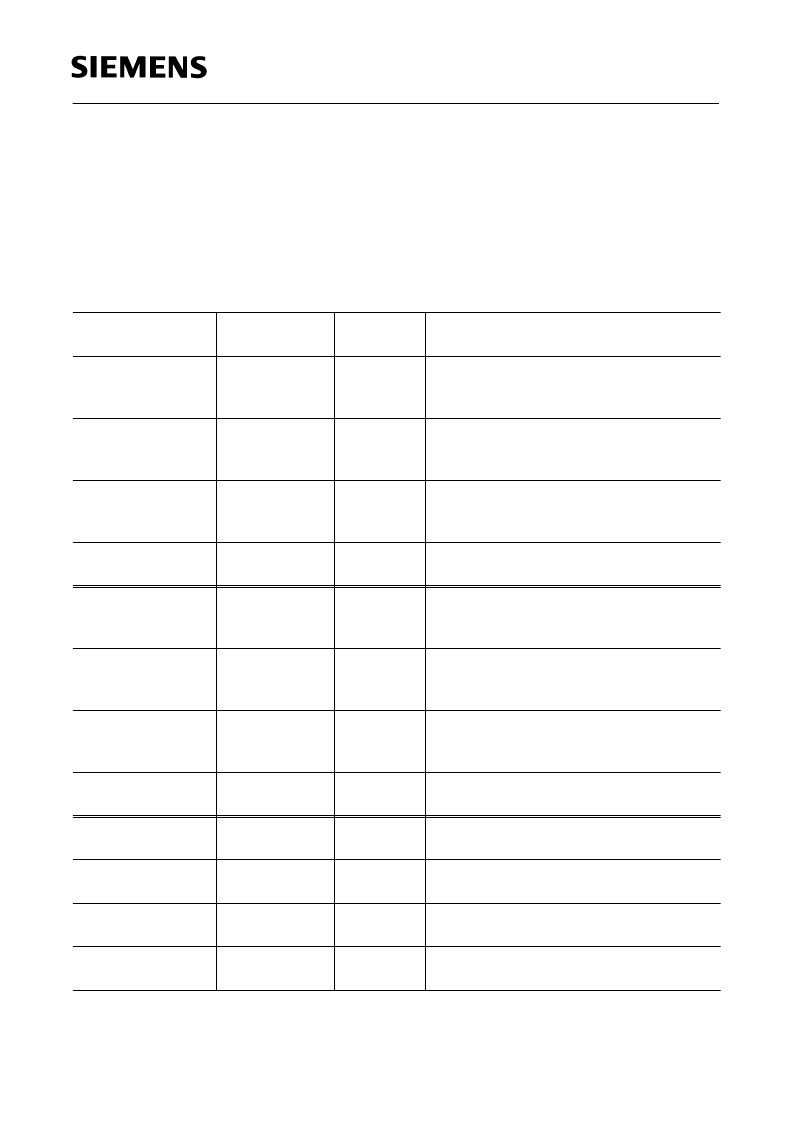

Ordering Information

Type

Ordering Code Package

Description

(8-Bit CMOS microcontroller)

for external memory (12 MHz)

SAB-C501G-LN

SAB-C501G-LP

SAB-C501G-LM

SAB-C501G-L24N

SAB-C501G-L24P

SAB-C501G-L24M

SAB-C501G-L40N

SAB-C501G-L40P

SAB-C501G-L40M

SAF-C501G-L24N

SAF-C501G-L24P

SAB-C501G-1RN

SAB-C501G-1RP

SAB-C501G-1RM

SAB-C501G-1R24N

SAB-C501G-1R24P

SAB-C501G-1R24M

SAB-C501G-1R40N

SAB-C501G-1R40P

SAB-C501G-1R40M

SAF-C501G-1R24N

SAF-C501G-1R24P

SAB-C501G-1EN

SAB-C501G-1EP

SAF-C501G-1EN

SAF-C501G-1EP

SAB-C501G-1E24N

SAB-C501G-1E24P

SAF-C501G-1E24N

SAF-C501G-1E24P

Q67120-C969

Q67120-C968

Q67127-C970

Q67120-C1001

Q67120-C999

Q67127-C1014

Q67120-C1002

Q67120-C1000

Q67127-C1009

Q67120-C1011

Q67120-C1010

Q67120-DXXX

Q67120-DXXX

Q67127-DXXX

Q67120-DXXX

Q67120-DXXX

Q67127-DXXX

Q67120-DXXX

Q67120-DXXX

Q67127-DXXX

Q67120-DXXX

Q67120-DXXX

Q67120-C1054

Q67120-C1056

Q67120-C2002

Q67120-C2003

Q67120-C2005

Q67120-C2006

Q67120-C2008

Q67120-C2009

P-LCC-44

P-DIP-40

P-MQFP-44

P-LCC-44

P-DIP-40

P-MQFP-44

P-LCC-44

P-DIP-40

P-MQFP-44

P-LCC-44

P-MQFP-44

P-LCC-44

P-DIP-40

P-MQFP-44

P-LCC-44

P-DIP-40

P-MQFP-44

P-LCC-44

P-DIP-40

P-MQFP-44

P-LCC-44

P-DIP-40

P-LCC-44

P-DIP-40

P-LCC-44

P-DIP-40

P-LCC-44

P-DIP-40

P-LCC-44

P-DIP-40

for external memory (24 MHz)

for external memory (40 MHz)

for external memory (24 MHz)

ext. temp. – 40 C to 85 C

with mask-programmable ROM (12 MHz)

with mask-programmable ROM (24 MHz)

with mask-programmable ROM (40 MHz)

with mask-programmable ROM (24 MHz)

ext. temp. – 40 C to 85 C

with OTP memory (12 MHz)

with OTP memory (12 MHz))

ext. temp. – 40

with OTP memory (24 MHz)

C to 85

C

with OTP memory (24 MHz))

ext. temp. – 40

C to 85

C

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Q67127-C1063 | 8-Bit CMOS Microcontroller |

| Q67127-C1071 | 8-Bit CMOS Microcontroller |

| Q67127-C1072 | 8-Bit CMOS Microcontroller |

| Q67127-C1081 | 8-Bit CMOS Microcontroller |

| Q67127-C1082 | 8-Bit CMOS Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| Q67127-C1063 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:8-Bit CMOS Microcontroller |

| Q67127-C1071 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:8-Bit CMOS Microcontroller |

| Q67127-C1072 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:8-Bit CMOS Microcontroller |

| Q67127-C1081 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:8-Bit CMOS Microcontroller |

| Q67127-C1082 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:8-Bit CMOS Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復。