- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296936 > QL2003-XPF144C Field Programmable Gate Array (FPGA) PDF資料下載

參數(shù)資料

| 型號: | QL2003-XPF144C |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場可編程門陣列(FPGA) |

| 文件頁數(shù): | 2/10頁 |

| 文件大?。?/td> | 182K |

| 代理商: | QL2003-XPF144C |

QL2003

3-14

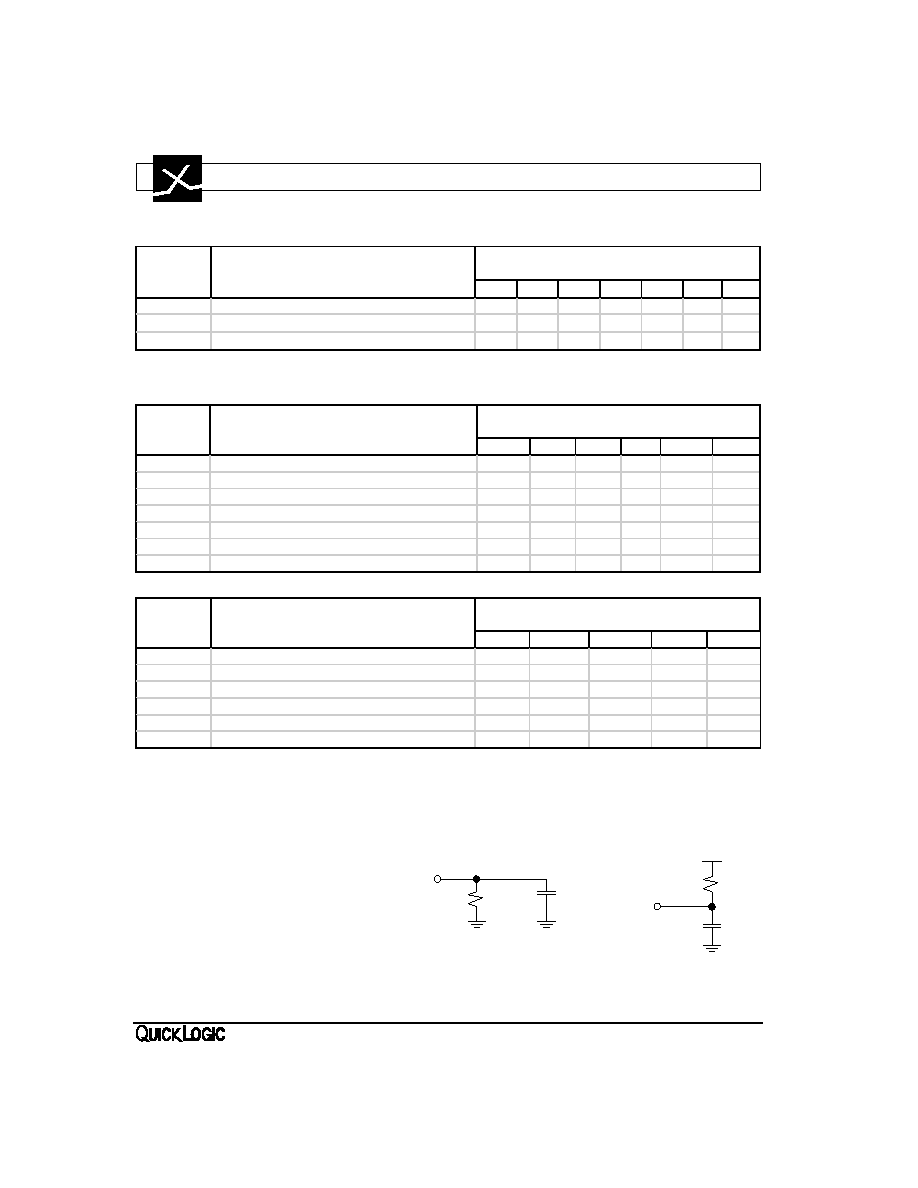

Clock Cells

Symbol

Parameter

Propagation Delays (ns)

Loads per Half Column [10]

1234

8

10

13

tACK

Array Clock Delay

2.2

2.3

2.4

2.5

2.6

tGCKP

Global Clock Pin Delay

1.2

tGCKB

Global Clock Buffer Delay

1.5

1.6

1.7

1.8

1.9

2.0

I/O Cells

Symbol

Parameter

Propagation Delays (ns)

Fanout [8]

12

3

4

8

10

tI/O

Input Delay (bidirectional pad)

1.8

2.1

2.4

2.7

3.9

4.6

tISU

Input Register Set-Up Time

4.8

tIH

Input Register Hold Time

0.0

tlOCLK

Input Register Clock To Q

0.8

1.1

1.4

1.7

2.9

3.6

tlORST

Input Register Reset Delay

0.7

1.0

1.3

1.6

2.8

3.5

tlESU

Input Register clock Enable Set-Up Time

4.1

tlEH

Input Register Clock Enable Hold Time

0.0

Symbol

Parameter

Propagation Delays (ns)

Output Load Capacitance (pF)

30

50

75

100

150

tOUTLH

Output Delay Low to High

2.6

3.0

3.6

4.1

5.2

tOUTHL

Output Delay High to Low

2.8

3.3

3.9

4.5

5.7

tPZH

Output Delay Tri-state to High

2.1

2.6

3.1

3.7

4.8

tPZL

Output Delay Tri-state to Low

2.6

3.3

4.1

4.9

6.5

tPHZ

Output Delay High to Tri-State [11]

2.9

tPLZ

Output Delay Low to Tri-State [11]

3.3

Notes:

[10]

The array distributed networks consist of 48 half columns and the global distributed networks consist of

52 half columns, each driven by an independent buffer. The number of half columns used does not affect

clock buffer delay. The array clock has up to 10 loads per half column. The global clock has up to 13

loads per half column.

[11]

The following loads are used for tPXZ:

5 pF

1K

5 pF

1K

tPHZ

tPLZ

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| QL2003-XPF144I | Field Programmable Gate Array (FPGA) |

| QL2003-XPL84C | Field Programmable Gate Array (FPGA) |

| QL2003-XPL84I | Field Programmable Gate Array (FPGA) |

| QL2005-0PF144C | Field Programmable Gate Array (FPGA) |

| QL2005-0PF144I | Field Programmable Gate Array (FPGA) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| QL2003-XPF144I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| QL2003-XPL84C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:3.3V and 5.0V pASIC-R 2 FPGA Combining Speed, Density, Low Cost and Flexibility |

| QL2003-XPL84I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:3.3V and 5.0V pASIC-R 2 FPGA Combining Speed, Density, Low Cost and Flexibility |

| QL2005-0PF144C | 制造商:QuickLogic Corporation 功能描述: |

| QL2005-0PF144I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

發(fā)布緊急采購,3分鐘左右您將得到回復。