- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361317 > QS5LV919133Q (INTEGRATED DEVICE TECHNOLOGY INC) 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER PDF資料下載

參數(shù)資料

| 型號: | QS5LV919133Q |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| 中文描述: | 5LV SERIES, PLL BASED CLOCK DRIVER, 7 TRUE OUTPUT(S), 1 INVERTED OUTPUT(S), PDSO28 |

| 封裝: | QSOP-28 |

| 文件頁數(shù): | 10/12頁 |

| 文件大小: | 98K |

| 代理商: | QS5LV919133Q |

10

INDUSTRIAL TEMPERATURE RANGE

QS5LV919

3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

1.0ns

1.0ns

2.0V

0.8V

3.0V

0V

V

th

= 0.5V

DD

t

PW

t

R

t

F

CONTROL

INPUT

ENABLE

DISABLE

3V

0V

3.0V

V

OL

0V

t

PZL

OUTPUT

NORMALLY

LOW

OUTPUT

NORMALLY

HIGH

SWITCH

OPEN

SWITCH

CLOSED

0.3V

0.3V

t

PZH

t

PLZ

t

PHZ

V

OH

300

30pF

7.0V

OUTPUT

V

DD

OUTPUT

300

100

100

2.0V

0.8V

3.0V

0V

0.5V

DD

0.5V

DD

0.5V

DD

0.5V

DD

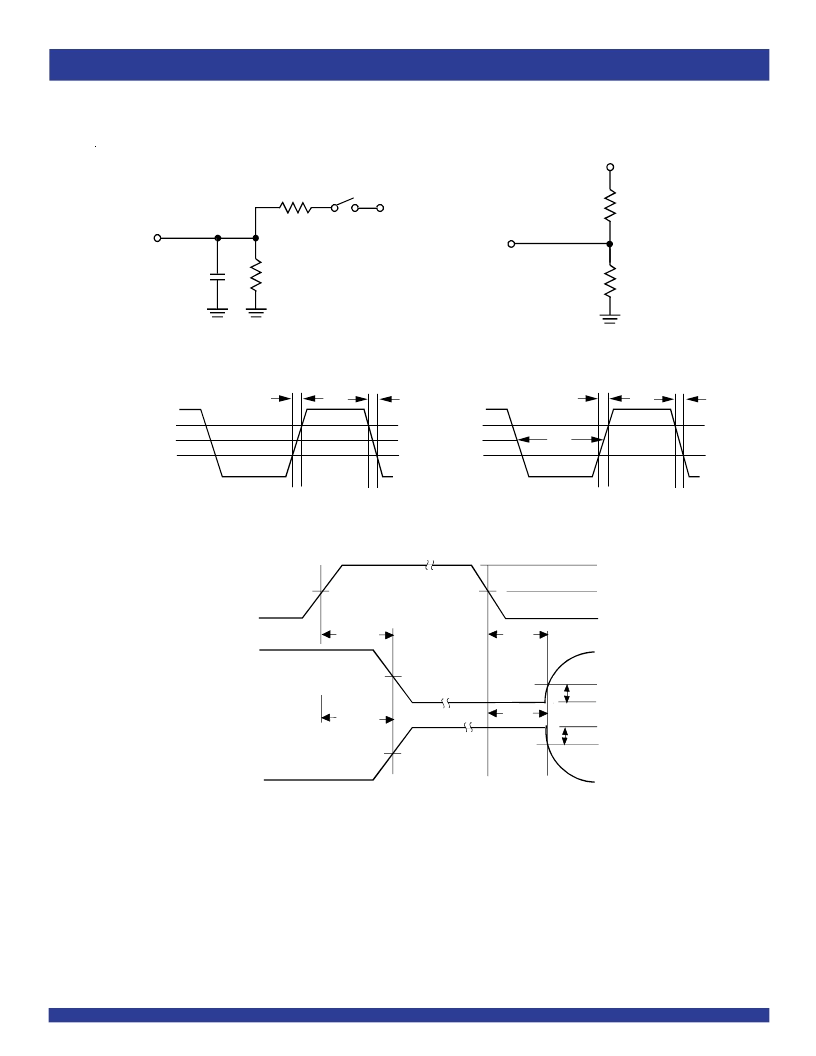

AC TEST LOADS AND WAV EFORMS

TEST CIRCUIT 1

LVTTL INPUT TEST WAVEFORM

LVTTL OUTPUT WAVEFORM

TEST CIRCUIT 2

ENABLE AND DISABLE TIMES

TEST CIRCUIT 1 is used for output enable/disable parameters.

TEST CIRCUIT 2 is used for all other timng parameters.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| QS5LV919160J | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV919160Q | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV91955J | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV91955Q | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV91970J | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| QS5LV919-133Q | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 28-Pin QSOP Tube |

| QS5LV919-133Q8 | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 28-Pin QSOP T/R |

| QS5LV919-133QG | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 28-Pin QSOP Tube |

| QS5LV919-133QG8 | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 28-Pin QSOP T/R |

| QS5LV919160J | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。