- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361317 > QS5LV91955J (INTEGRATED DEVICE TECHNOLOGY INC) 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER PDF資料下載

參數(shù)資料

| 型號(hào): | QS5LV91955J |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| 中文描述: | 5LV SERIES, PLL BASED CLOCK DRIVER, 7 TRUE OUTPUT(S), 1 INVERTED OUTPUT(S), PQCC28 |

| 封裝: | PLASTIC, LCC-28 |

| 文件頁(yè)數(shù): | 3/12頁(yè) |

| 文件大?。?/td> | 98K |

| 代理商: | QS5LV91955J |

3

INDUSTRIAL TEMPERATURE RANGE

QS5LV919

3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

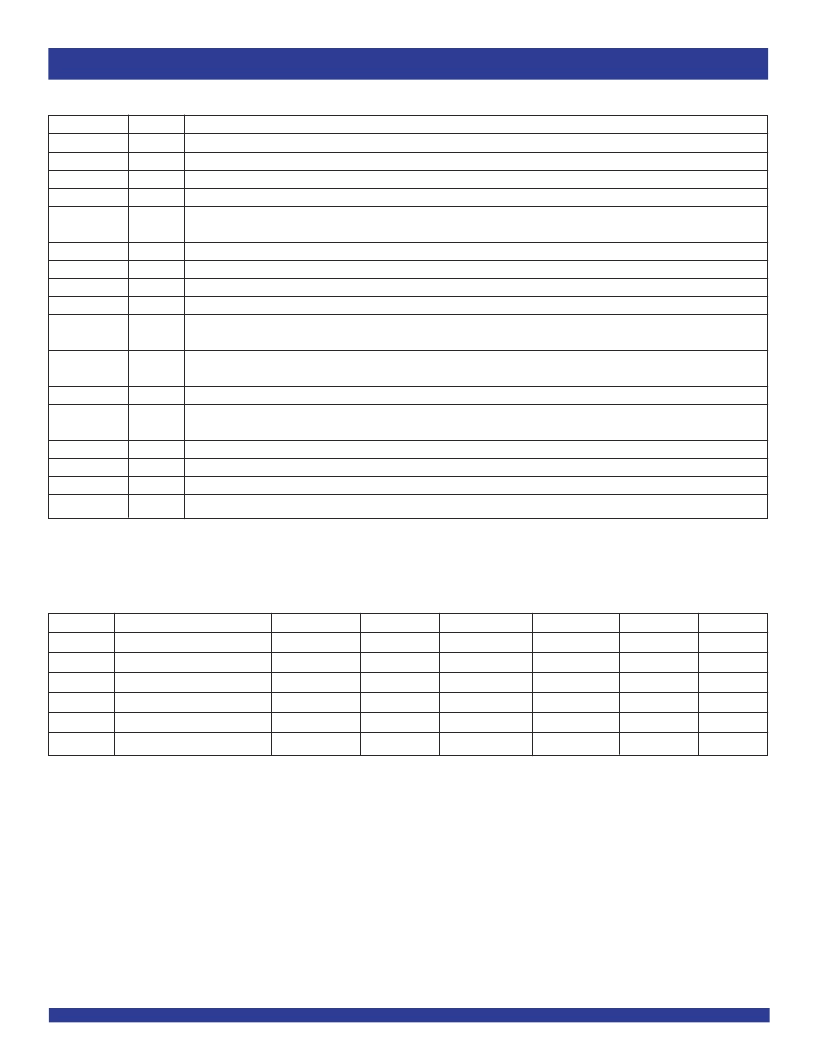

PIN DESCRIPTION

Pin Name

SYNC

0

SYNC

1

REF_SEL

FREQ_SEL

FEEDBACK

I/O

I

I

I

I

I

Description

Reference clock input

Reference clock input

Reference clock select. When 1, selects SYNC

1

. When 0, selects SYNC

0

.

VCO frequency select. For choosing optimal VCO operating frequency depending on input frequency.

PLL feedback input which is connected to a user selected output pin. External feedback provides flexibility for different

output frequency relationships. See the Frequency Selection Table for more information.

Clock outputs

Clock output. Matched in frequency, but inverted with respect to Q.

Clock output. Matched in phase, but frequency is double the Q frequency.

Clock output. Matched in phase, but frequency is half the Q frequency.

PLL lock indication signal. 1 indicates positive lock. 0 indicates that the PLL is not locked and outputs may not be

synchronized to the inputs.

Output enable/asynchronous reset. Resets all output registers. When 0, all outputs are held in a tri-stated condition. When

1, outputs are enabled.

PLL enable. Enables and disables the PLL. Useful for testing purposes.

When

PE

is LOW, outputs are synchronized with the positive edge of SYNC. When HIGH, outputs are synchronized with

the negative edge of SYNC.

Power supply for output buffers.

Power supply for phase lock loop and other internal circuitries.

Ground supply for output buffers.

Ground supply for phase lock loop and other internal circuitries.

Q

0

-Q

4

Q

5

2xQ

Q/2

LOCK

O

O

O

O

O

OE/

RST

I

PLL_EN

PE

I

I

V

DD

AV

DD

GND

AGND

—

—

—

—

OUTPUT FREQUENCY SPECIFICATIONS

Industrial: T

A

= –40°C to +85°C, AV

DD

/ V

DD

= 3.3V ± 0.3V

Symbol

Description

– 55

– 70

– 100

– 133

– 160

Units

F

MAX_2XQ

F

MAX_Q

F

MAX_Q/2

F

MIN_2XQ

F

MIN_Q

F

MIN_Q/2

Max Frequency, 2xQ

Max Frequency, Q

0

- Q

4

, Q

5

Max Frequency, Q/2

Mn Frequency, 2xQ

Mn Frequency, Q

0

- Q

4

, Q

5

Mn Frequency, Q/2

55

27.5

13.75

20

10

5

70

35

17.5

20

10

5

100

50

25

20

10

5

133

66.5

33.25

20

10

5

160

80

40

20

10

5

MHz

MHz

MHz

MHz

MHz

MHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| QS5LV91955Q | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV91970J | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV91970Q | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV919 | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV919100J | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| QS5LV91955Q | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV91970J | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV91970Q | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV931 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV93150Q | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。